Dear TI team,

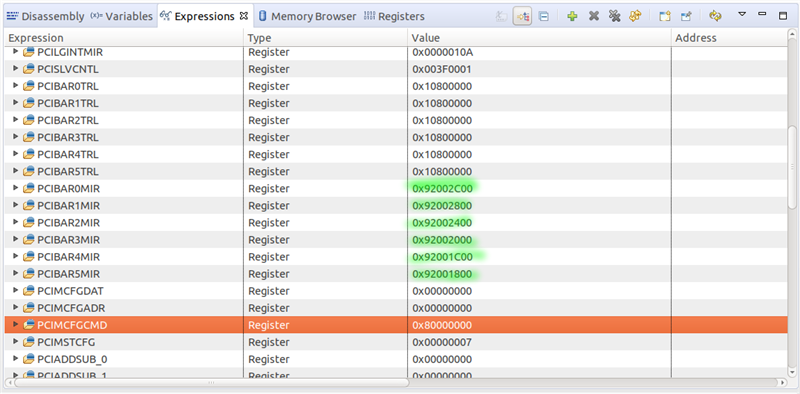

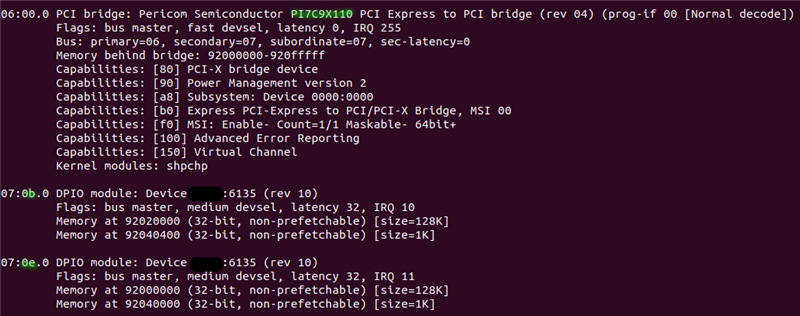

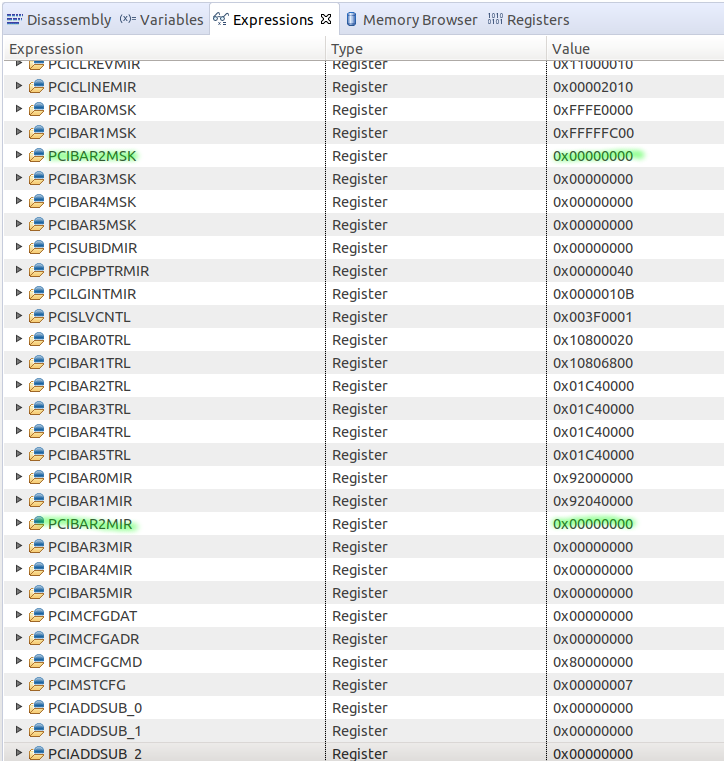

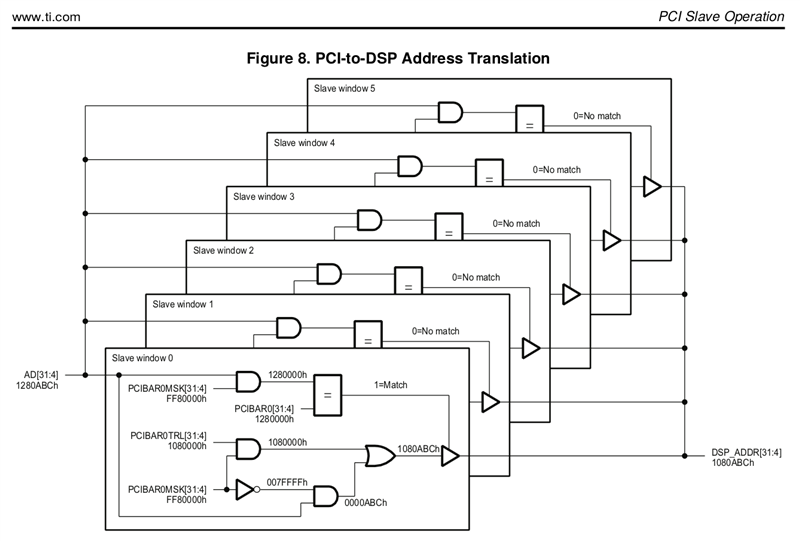

I am working with TMS320C6424 PCI module. I managed to develop Linux driver and firmware capable of read ADC data. I used only 2 of 6 BARs. I used to disable BARn by PCIBARnMSK = 0.

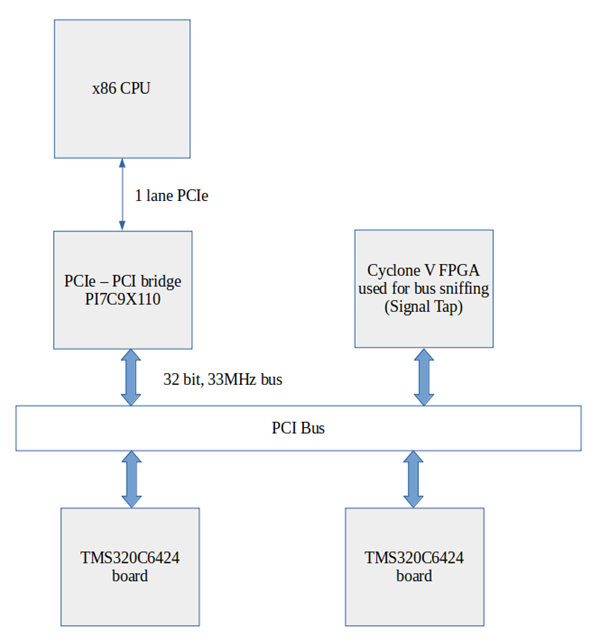

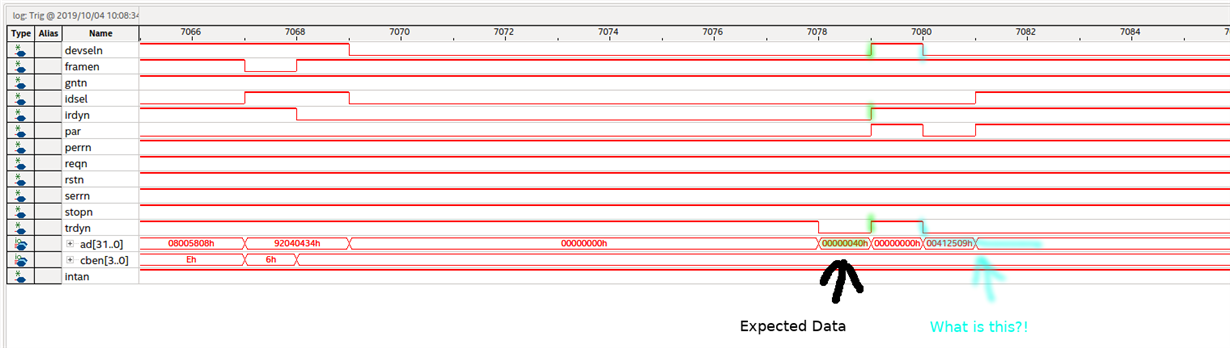

My firmware worked well until I connected 2 TMS320C6424 in same PCI bus. After a few days of debugging I found out that PTRDY_N signal is driven by both DSP in opposite directions. Here is a picture of bus signal:

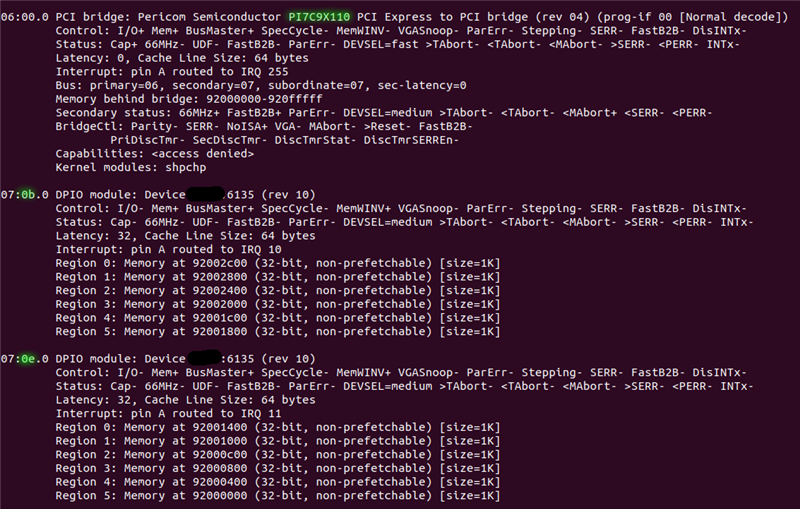

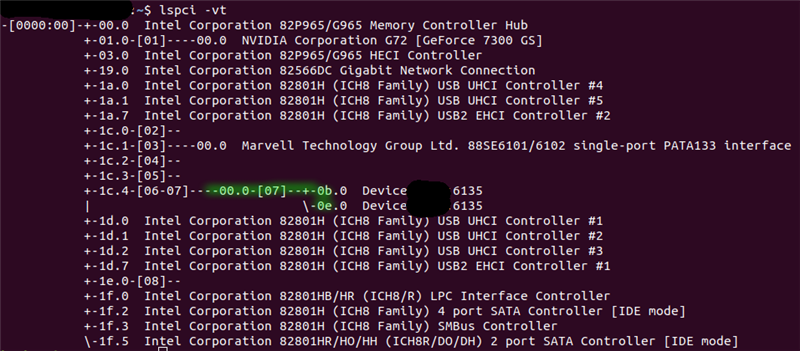

If I enable all BARs problem disappears. So far I can use two TMS320C6424 on one bus by configuring all 6 BARs to same size and same location. Looks like if at least one of PCIBARnMSK registers is set to 0 PCI communication gets broken.

Could you please confirm whether this is a bug in the TMS320C6424? What is a proper way to disable a BAR in TMS320C6424?

Regards,

Kirill