Part Number: AM3352

Hi champs,

customer has reached a reproducible state in which the GPMC controller does not behave in conformity with the system.

The first accesses proceed as expected correctly, only after a certain time the GMPC controller does not seem to have the need

to operate the Write_Enable signal.

Question:

What can cause the GPMC controller to go completely out of step and ignore the GPMC settings?

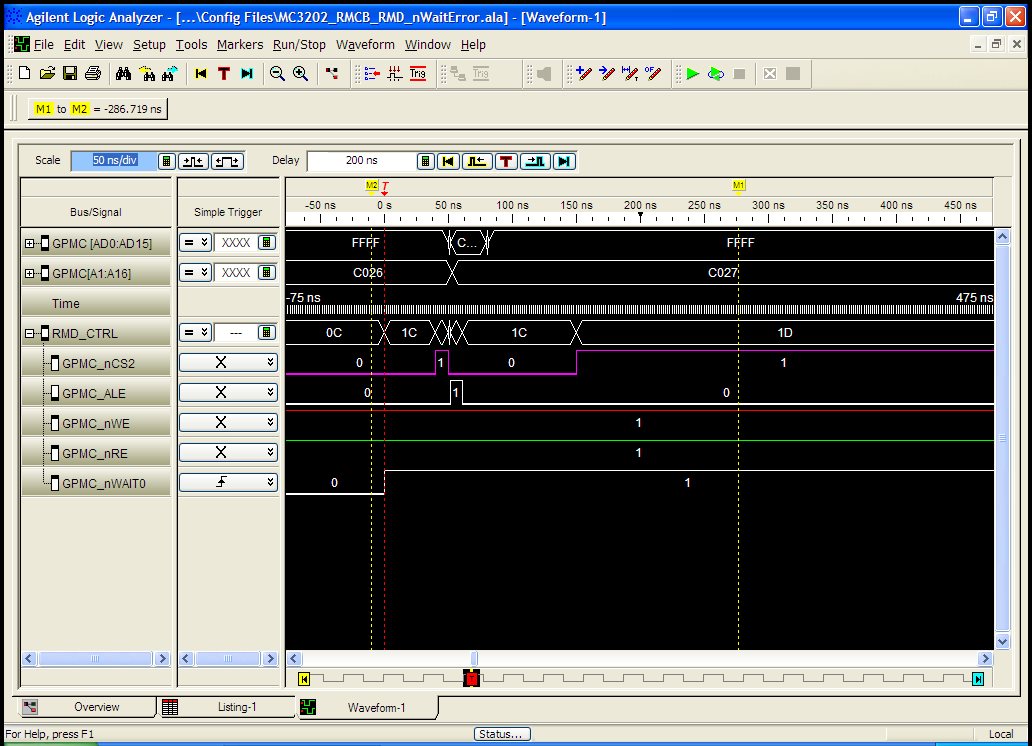

Below the representation of the error image:

Following is the analog measurement of the write_enable signal, the signal is not pulled low by the GPMC controller:

A review of the timing both before the situation and in case of error shows no manipulation of

GPMC timing what this could have been explained.

Another insight,

This could be avoided by adding an ARM-DSB (Data Synchronization Barrier) command.

The problem is that this is not possible in the DMA transfer.

Can you help us here?