Hi,

I have a question about HyperBus 100 MHz Switching Characteristics.

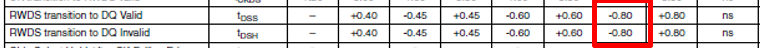

According to JEDEC the RWDS transition to DQ is -0.8 ns minimum

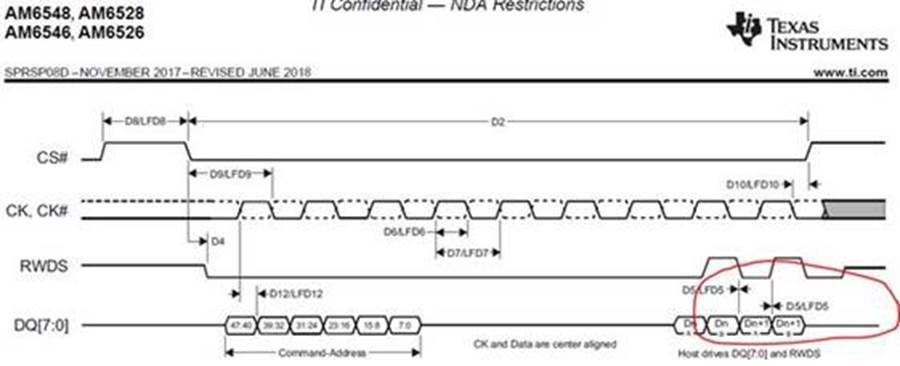

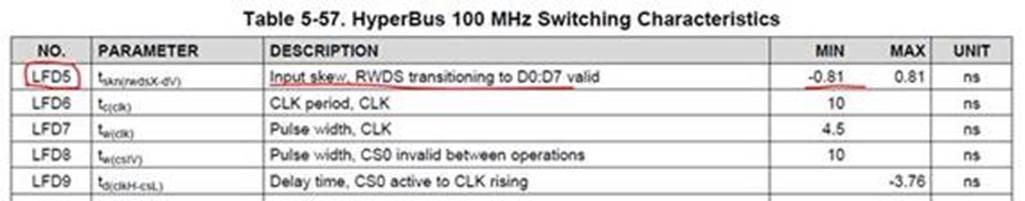

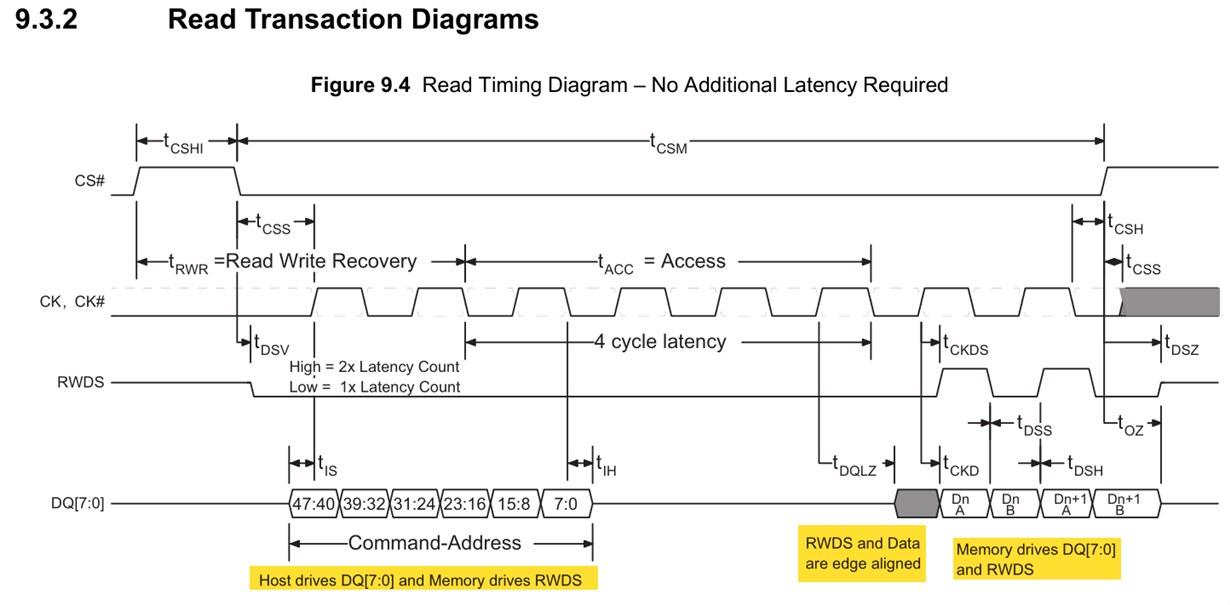

According to datasheet AM6548, RWDS transition to DQ is -0.81 ns (“tsetup input” and “thold input” RWDS to DQ )

Please can you confirm LFD5 = -0.81ns?

The timing is too tight (10ps will be consumed by interconnection delay like traces, vias, ...).

Does AM6548 has an internal delay per pin or of RWDS for HyperBUS to achieve good setup and hold margins on read operations?

Many thanks and best regards

Marcus