Tool/software: Code Composer Studio

Hi,

I use GPMC module of AM5708 with Nor-flash MT28EW01 in simple non-multiplexed mode. In single read mode GPMC module works fine.

Configuration of GPMC in this case:

0x00001010, // GPMC_CONFIG1_i (sets signal control parameters)

0x001E1E80, // GPMC_CONFIG2_i (CS signal timing parameter configuration)

0x00000000, // GPMC_CONFIG3_i (nADV signal timing parameter configuration)

0x0F071A80, // GPMC_CONFIG4_i (nWE and nOE signals timing parameter configuration)

0x030D1F1F, // GPMC_CONFIG5_i (RdAccessTime and CycleTime timing parameters configuration)

0x8F070000, // GPMC_CONFIG6_i (WrAccessTime, WrDataOnADmuxBus, Cycle2Cycle and BusTurnAround parameters configuration)

0x00000840, // GPMC_CONFIG7_i (CS address mapping configuration)

..........................................................

volatile __int64_t *BASE_ADDR_64 = FLASH_BASE_ADDRESS;

for(dwCnt = 0;dwCnt < (dwDeviceSize / 4);dwCnt++)

{

n64TmpBuf = BASE_ADDR_64[dwCnt];

UARTConfigPutc(DEBUG_UART_BASE, n64TmpBuf);

UARTConfigPutc(DEBUG_UART_BASE, n64TmpBuf >> 8);

UARTConfigPutc(DEBUG_UART_BASE, n64TmpBuf >> 16);

UARTConfigPutc(DEBUG_UART_BASE, n64TmpBuf >> 24);

UARTConfigPutc(DEBUG_UART_BASE, n64TmpBuf >> 32);

UARTConfigPutc(DEBUG_UART_BASE, n64TmpBuf >> 40);

UARTConfigPutc(DEBUG_UART_BASE, n64TmpBuf >> 48);

UARTConfigPutc(DEBUG_UART_BASE, n64TmpBuf >> 56);

}

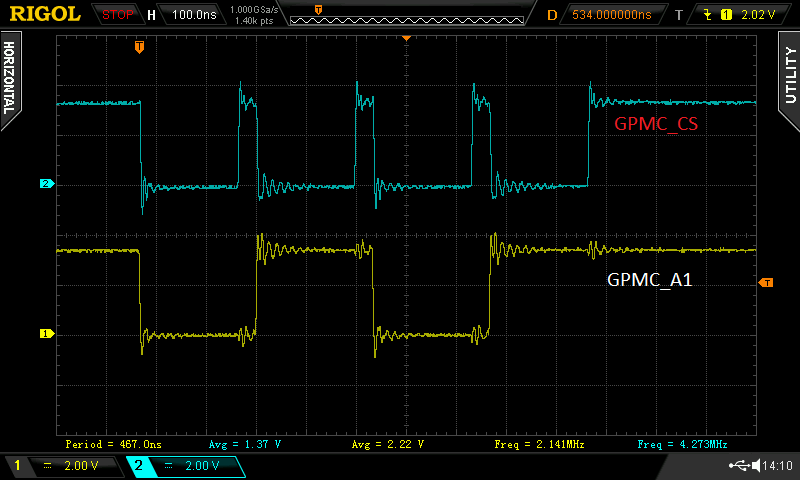

Below you can see the result of the code snippet shown above:

On the oscillogram we can see four separated read cycles through 16-bit data bus.

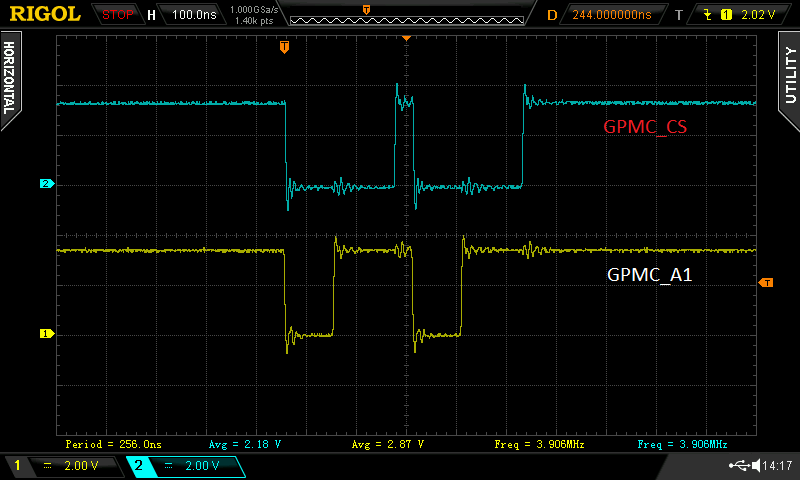

In mode READMULTIPLE the same code snippet give the following result on bus:

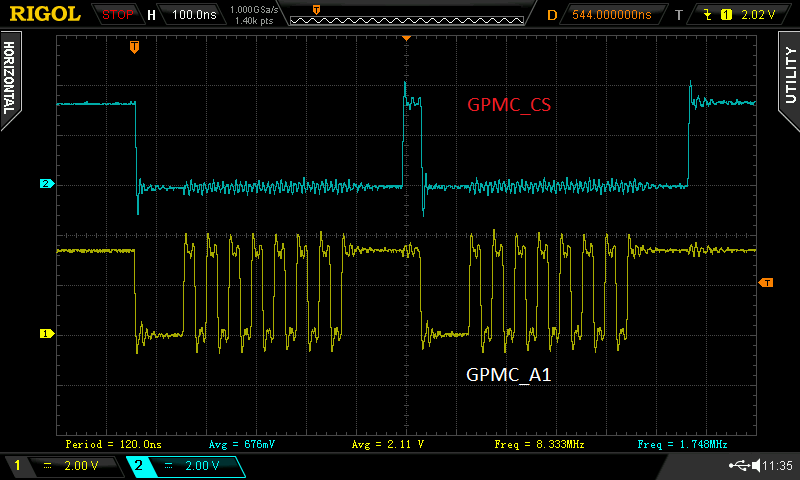

In this case we setup GPMC as follow:

0x40001010, // GPMC_CONFIG1_i (sets signal control parameters) x2 latencies

0x001E1E80, // GPMC_CONFIG2_i (CS signal timing parameter configuration)

0x00000000, // GPMC_CONFIG3_i (nADV signal timing parameter configuration)

0x0F071A80, // GPMC_CONFIG4_i (nWE and nOE signals timing parameter configuration)

0x030D1F1F, // GPMC_CONFIG5_i (RdAccessTime and CycleTime timing parameters configuration)

0x8F070000, // GPMC_CONFIG6_i (WrAccessTime, WrDataOnADmuxBus, Cycle2Cycle and BusTurnAround parameters configuration)

0x00000840, // GPMC_CONFIG7_i (CS address mapping configuration)

On last picture we see that the address line a1 is not incrementing though the data read correctly but more slowly than single read.

How can I read entire 4-words page? Maybe setup of GPMC is wrong or incomplete?

Possibly we need point to compiler additional directives before read operation?

Regards, Andrei