hi,

NAND booting on DRA71x issue

Please help how to solve the nand boot issue.

SOC: DRA81x, SDK:ti-processor-sdk-linux-automotive-dra7xx-evm-03_02_00_03 NADN:MT29F1G08ABAEAWP (2048+64bytes) CCS: Code Composer Studio 6.1.2

SYSBOOT[0:15] = 10011100 10010001. [0:3] = 1001. [4:5]=11

The MLO file can boot from QSPI flash, GP header + MLOfile write to nand flash, it can not boot.

struct Nand_Gp_Header {

unsigned int size;

unsigned int code_point;

};

gpheader.size = statbuf.st_size+sizeof(struct Nand_Gp_Header);

gpheader.code_point = 0x40300000;

[ 1.539675] 0x000000000000-0x000003c00000 : "NAND.ROOTFS"

[ 1.578282] 0x000003c00000-0x000007800000 : "NAND.BACK"

flash_erase /dev/mtd0 0 0

nandwrite /dev/mtd0 MLOfile

cold reset, but Soc cannot boot, console do not have any print!!!

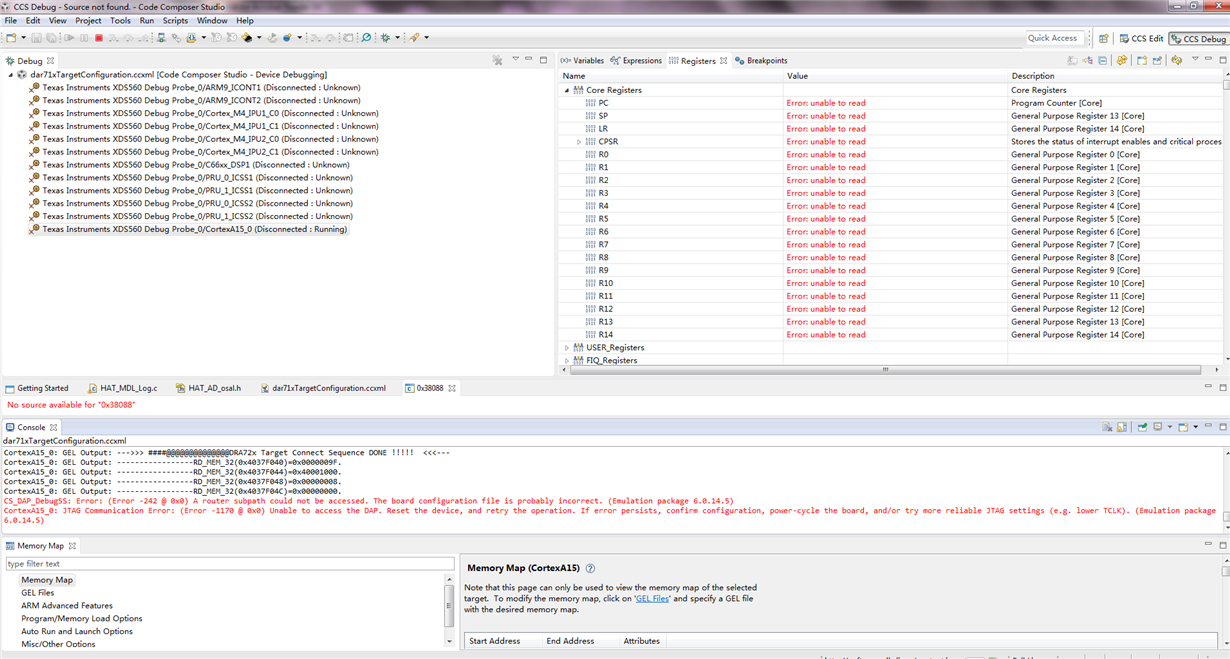

So. I use CCS tools to debug it.

On data sheet 33.3.9 , Trace registers have been print, Is there any useful information?