Part Number: AM5718

Hi,

I have interfaced DDR3L Part no: MT41K256M16TW-107:P (part no mentioned in AM5718 BOM) to AM5718.

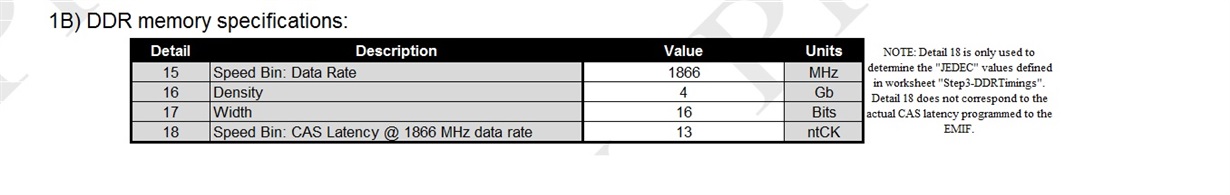

I am trying to create EMIF configuration using the EMIF spreadsheet. Attached is the spread sheet. I have modified the following section as  shown. Latency I have updated to 13ns as per the data sheet of memory.

shown. Latency I have updated to 13ns as per the data sheet of memory.

On Step3 DDRtimings I see parameter tCKESR final bit value shaded in yellow. Is this OK??

SpreaEMIF_RegisterConfig.rardsheet

DDR datasMT41K256M16TW-107 XITP TR.pdfheet