I am using the Logic SOM-M1 on a custom board using the Logic BSL drivers. During the initilzation process of the I2C1 the following code is used (from evmomapl138_i2c.c):

==========================================================

// configure i2c for master transmit mode and release from reset.

i2c->ICMDR = STT | MST | ICMDR_FREE | TRX | IRS;

====================================================

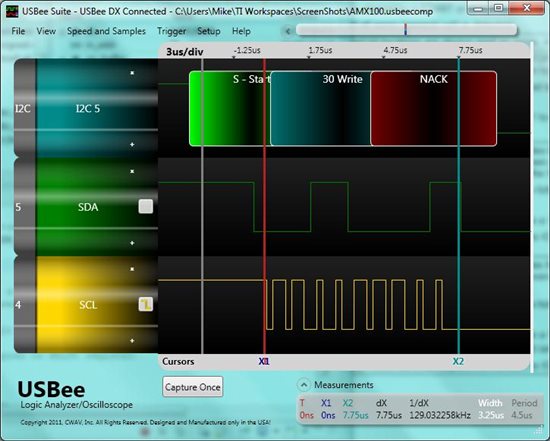

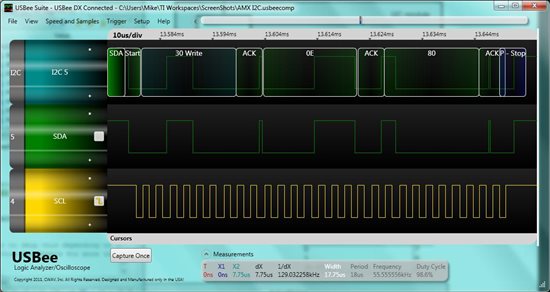

After this step is executed the SCL and SDA lines are both pulled low and remain low. This doesn't seem right to me. The code then goes into a loop attempting to send a byte of data out on SDA but gets stuck in a timeout loop waiting for ICSTR to become ready.

===================================================

// transmit data one byte at a time.

for(i = 0; i < in_length; i++)

{ i2c->ICDXR = src_buffer[i];

// wait for data to be copied to shift register.

cnt = 0;

do

{ (cnt++ > I2C_TIMEOUT)

{ // timed out waiting for data...reinit and return error. I2C_init(i2c, g_clock_rate); (ERR_TIMEOUT);

} } (!CHKBIT(i2c->ICSTR, ICXRDY)); ================================================== Data never shows up on the SDA line and there is no SCL. The SDA and SCL lines are connected to a AIC3204 and have 1K pullups on the SOM board. Cany anyone give guidance on what may be happening? (Also, I am obviously not cutting and pasting code properly from ccs4 into this forum window. Is there a "correct" way to do this that doesn't trash the format?) Thx, MikeH