Hello,

we are using the AM5728. On the A15 cores runs Linux, on both DSP's are running highly optimized bare metal real time applications (motion control).

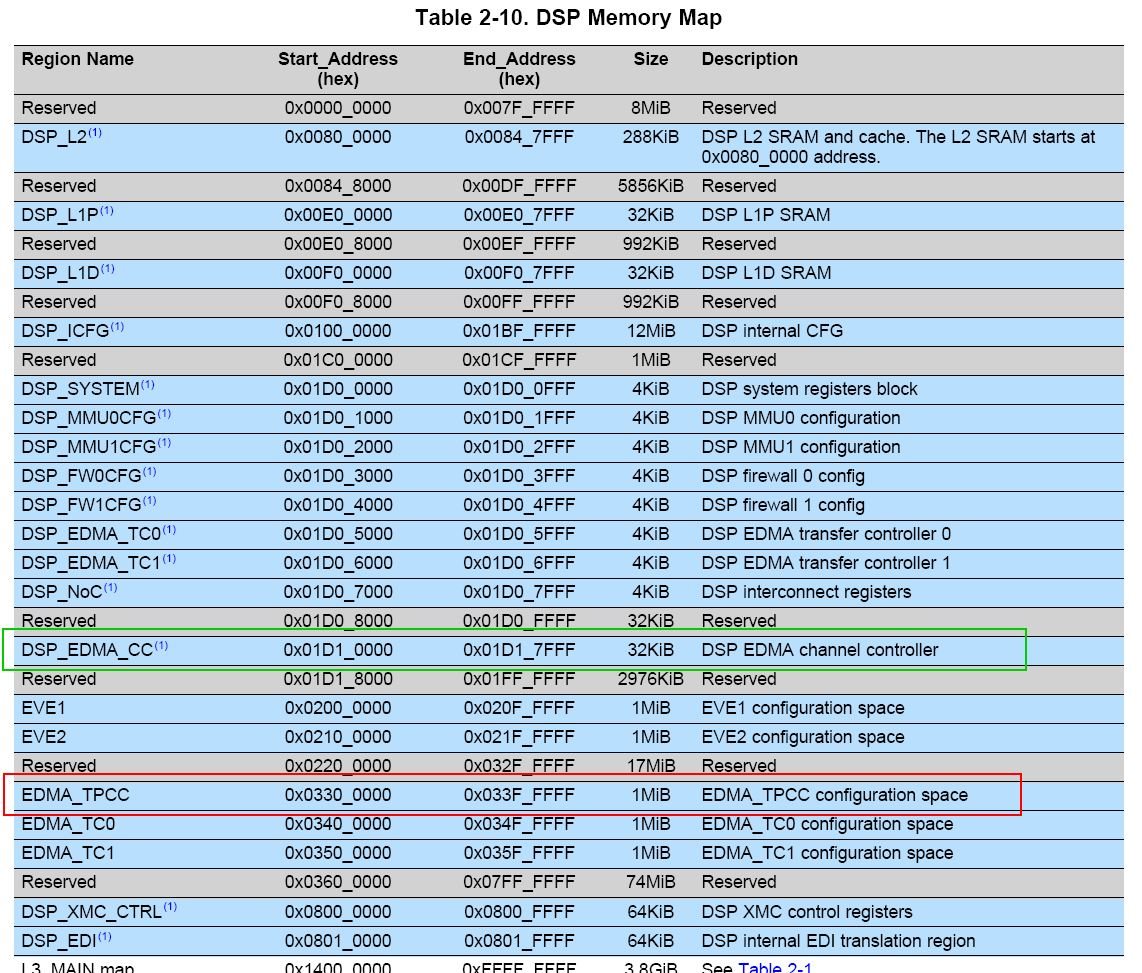

The DSP1 is in need to transfer data from peripherals to its memory by DMA. The EDMA is used for this.

Because of some problems with the EDMA transfer I reduced the desired functionality to a very simple one dimensional manual tiggered memory to memory EDMA example with completion polling to demonstrate my problem.

First I used the system level EDMA to transfer the data. Please note the section .dma_mem is located at the OCMC_RAM1. It works as expected.

//#define EDMA_CC_BASE SOC_DSP1_EDMA_CC_BASE

#define EDMA_CC_BASE SOC_EDMA_TPCC_BASE_VIRT

#pragma DATA_SECTION(".dma_mem")

char srcBuff[16] = "Hello~world~123";

#pragma DATA_SECTION(".dma_mem")

char dstBuff[16];

dma_test( 5, 5, 0 );

void dma_test( uint32_t ch_num, uint32_t tcc_num, uint32_t evtq_num )

{

EDMAsetRegion( 0 );

EDMA3Init( EDMA_CC_BASE, EVT_QUEUE_NUM );

if( EDMA3RequestChannel( EDMA_CC_BASE, EDMA3_CHANNEL_TYPE_DMA, ch_num, tcc_num, evtq_num ) == 0 )

{

TRACE( true, (TRACE_ERR, "EDMA channel request failed") );

}

EDMA3CCPaRAMEntry Param =

{

.srcAddr = (uint32_t)srcBuff,

.destAddr = (uint32_t)dstBuff,

.aCnt = ARRAYSIZE(srcBuff),

.bCnt = 1,

.cCnt = 1,

.srcBIdx = 1,

.destBIdx = 1,

.srcCIdx = 1,

.destCIdx = 1,

.linkAddr = 0xFFFFU,

.opt = (EDMA3_OPT_TCINTEN_MASK | EDMA3_OPT_ITCINTEN_MASK | ((tcc_num << EDMA3_OPT_TCC_SHIFT) & EDMA3_OPT_TCC_MASK))

};

EDMA3SetPaRAM( EDMA_CC_BASE, ch_num, &Param );

EDMA3EnableTransfer( EDMA_CC_BASE, ch_num, EDMA3_TRIG_MODE_MANUAL );

// poll on complete

if(tcc_num < 32)

{

while( (EDMA3GetIntrStatus(EDMA_CC_BASE) & (0x1 << tcc_num)) != (0x1 << tcc_num) ) ;

}

else

{

while( (EDMA3IntrStatusHighGet(EDMA_CC_BASE) & (0x1 << (tcc_num - 32))) != (0x1 << (tcc_num - 32)) ) ;

}

}

Now I want to to ensure the Linux EDMA usage and the DSP1 EDMA usage will not conflict. Therefore DSP1 shall not use the system EDMA but the DSP1 EDMA.

But when changing EDMA_CC_BASE to SOC_DSP1_EDMA_CC_BASE something gets wrong.

It compiles, it runs, it generates no error, also the transfer seems to work because the transfer completion will be set shortly after the transmission has been start, but the destination memory is not filled with the data as this happens with the system EDMA.

What has to be considered when using DSP1 EDMA instead of system EDMA?

I read the TRM carefully but find not the reason for this malfunction.

Thank you very much.

Regards Dirk

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.