Booting J721E SoM with SD-Card MMC1 fails, if Hardware is not the TI Evalboard J721EXCP01EVM.

I have my own hardware to plug-in the TDA4 SoM (from the TI J7X Evalboard Kit)

The SD-Card reader is patched exactly the same as on the Evalboard (Schematic Sheet 23) to the SoM.

The SoM does NOT boot to this SD-Card and does not print any message to the console UART.

The same uSD Card connected to the Evalboard does boot and start-up as expected.

When I boot my own hardware to OSPI Flash, U-BOOT is starting and tries to boot from

SD-Card (MMC1), all files and configuration can be read from the SD-Card.

The only difference is the error-message "Card did not respond to voltage select!"

We are not able to find the reason for this message in the software.

Another difference is the transfer speed, my SD-Card is slower, because it is patched to

the TDA4 SoM module for testing purposes.

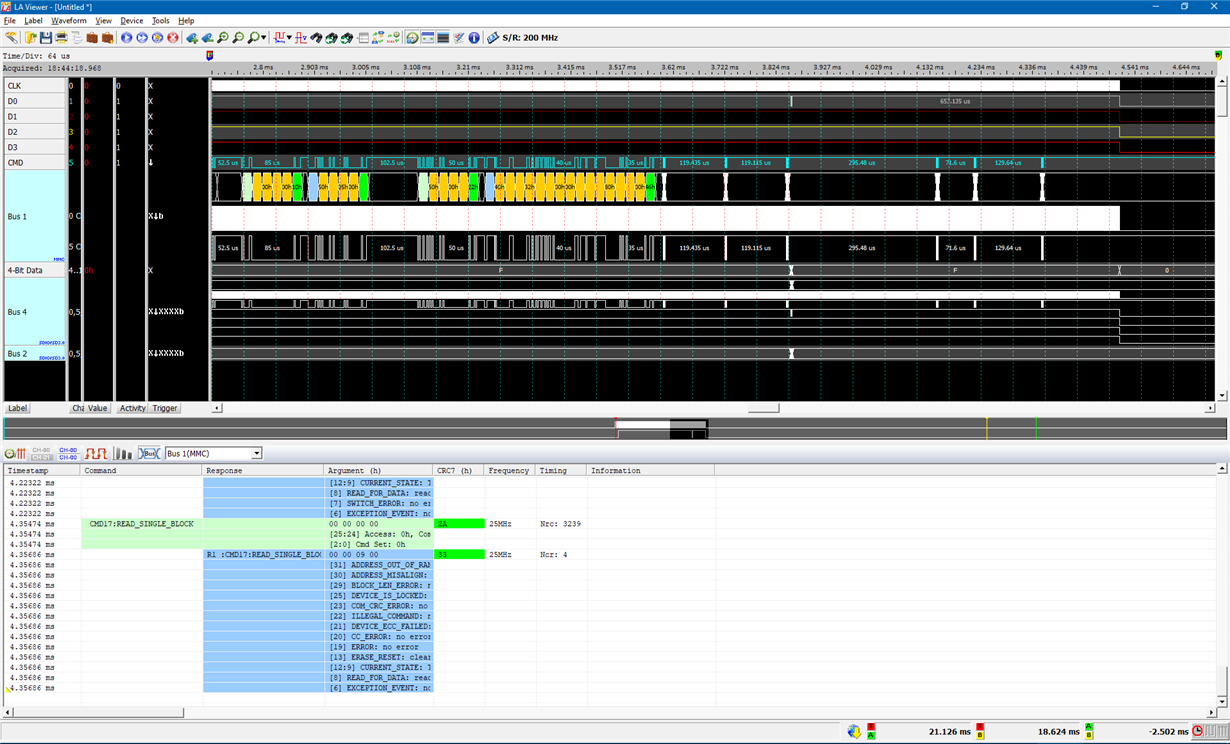

The Logic-Analyzer Traces show that the Bootloader is accessing the card and reading data in 4-bit mode.

Is there anything else beside the SD-Card, the SoM Bootloader ROM code requires to boot the SD-Card ?

<image is not copied>

SD-Card Boot from SoM, repeats several times, but SoM does not start

Log: EVM

*********************************************

U-Boot SPL 2019.01-g66126341c8 (Dec 11 2019 - 23:01:49 +0000)

SYSFW ABI: 2.6 (firmware rev 0x0013 '19.8.0-v2019.08-3-g8644f (Terri')

Trying to boot from MMC2

Loading Environment from MMC... *** Warning - No MMC card found, using default environment

Remoteproc 2 started successfully

** File not found /lib/firmware/j7-mcu-r5f0_0-fw **

Starting ATF on ARM64 core...

NOTICE: BL31: v2.1(release):ti2019.02-rc4

NOTICE: BL31: Built : 22:48:11, Dec 11 2019

I/TC:

I/TC: OP-TEE version: ti2019.02-89-ge5a8779-dev (gcc version 8.3.0 (GNU Toolchain for the A-profile Architecture 8.3-2019.03 (arm-rel-8.36))) #1 Wed Dec 11 22:59:07 UTC 2019 aarch64

I/TC: Initialized

U-Boot SPL 2019.01-g66126341c8 (Dec 11 2019 - 23:01:23 +0000)

Detected: J7X-BASE-CPB rev E3

Detected: J7X-VSC8514-ETH rev E2

Trying to boot from MMC2

U-Boot 2019.01-g66126341c8 (Dec 11 2019 - 23:01:23 +0000)

SoC: J721E PG 1.0

Model: Texas Instruments K3 J721E SoC

Board: J721EX-PM2-SOM rev E7

DRAM: 4 GiB

Flash: 0 Bytes

MMC: sdhci@4f80000: 0, sdhci@4fb0000: 1

Loading Environment from MMC... OK

In: serial@2800000

Out: serial@2800000

Err: serial@2800000

Detected: J7X-BASE-CPB rev E3

Detected: J7X-VSC8514-ETH rev E2

Net:

Warning: ethernet@046000000 using MAC address from ROM

eth0: ethernet@046000000

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc1 is current device

SD/MMC found on device 1

** Unable to read file boot.scr **

81 bytes read in 1 ms (79.1 KiB/s)

Loaded env from uEnv.txt

Importing environment from mmc1 ...

12364364 bytes read in 518 ms (22.8 MiB/s)

Load Remote Processor 3 with data@addr=0x80080000 12364364 bytes: Success!

** File not found /lib/firmware/j7-main-r5f1_0-fw **

9047884 bytes read in 377 ms (22.9 MiB/s)

Load Remote Processor 6 with data@addr=0x80080000 9047884 bytes: Success!

9046832 bytes read in 379 ms (22.8 MiB/s)

Load Remote Processor 7 with data@addr=0x80080000 9046832 bytes: Success!

11948304 bytes read in 499 ms (22.8 MiB/s)

Load Remote Processor 8 with data@addr=0x80080000 11948304 bytes: Success!

13338632 bytes read in 560 ms (22.7 MiB/s)

98400 bytes read in 5 ms (18.8 MiB/s)

3653 bytes read in 1 ms (3.5 MiB/s)

3742 bytes read in 2 ms (1.8 MiB/s)

## Flattened Device Tree blob at 82000000

Booting using the fdt blob at 0x82000000

Loading Device Tree to 00000000fdda6000, end 00000000fdec1fff ... OK

Log My own Hardware

***********************************************************

U-Boot SPL 2019.01-g66126341c8 (Dec 11 2019 - 23:01:49 +0000)

SYSFW ABI: 2.6 (firmware rev 0x0013 '19.8.0-v2019.08-3-g8644f (Terri')

Trying to boot from SPI

Loading Environment from MMC... spl: unsupported mmc boot device.

sdhci@4f80000 - probe failed: -19

spl: unsupported mmc boot device.

sdhci@4fb0000 - probe failed: -19

*** Warning - No MMC card found, using default environment

Loading rproc fw image from device 3 not supported!

Loading rproc fw image from device 3 not supported!

Starting ATF on ARM64 core...

NOTICE: BL31: v2.1(release):ti2019.02-rc4

NOTICE: BL31: Built : 22:48:11, Dec 11 2019

I/TC:

I/TC: OP-TEE version: ti2019.02-89-ge5a8779-dev (gcc version 8.3.0 (GNU Toolchain for the A-profile Architecture 8.3-2019.03 (arm-rel-8.36))) #1 Wed Dec 11 22:59:07 UTC 2019 aarch64

I/TC: Initialized

U-Boot SPL 2019.01-g66126341c8 (Dec 11 2019 - 23:01:23 +0000)

Trying to boot from SPI

U-Boot 2019.01-g66126341c8 (Dec 11 2019 - 23:01:23 +0000)

SoC: J721E PG 1.0

Model: Texas Instruments K3 J721E SoC

Board: J721EX-PM2-SOM rev E7

DRAM: 4 GiB

Flash: 0 Bytes

MMC: sdhci@4f80000: 0, sdhci@4fb0000: 1

Loading Environment from MMC... Card did not respond to voltage select!

*** Warning - No block device, using default environment

In: serial@2800000

Out: serial@2800000

Err: serial@2800000

Net: Could not get PHY for ethernet@046000000: addr 0

phy_connect() failed

eth-1: ethernet@046000000

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc1 is current device

SD/MMC found on device 1

** Unable to read file boot.scr **

81 bytes read in 2 ms (39.1 KiB/s)

Loaded env from uEnv.txt

Importing environment from mmc1 ...

Card did not respond to voltage select!

12364364 bytes read in 2003 ms (5.9 MiB/s)

Invalid seq: Enable primary core before loading secondary core

Load Remote Processor 3 with data@addr=0x80080000 12364364 bytes: Failed!

** File not found /lib/firmware/j7-main-r5f1_0-fw **

9047884 bytes read in 1463 ms (5.9 MiB/s)

Load Remote Processor 6 with data@addr=0x80080000 9047884 bytes: Success!

9046832 bytes read in 1465 ms (5.9 MiB/s)

Load Remote Processor 7 with data@addr=0x80080000 9046832 bytes: Success!

11948304 bytes read in 1933 ms (5.9 MiB/s)

Load Remote Processor 8 with data@addr=0x80080000 11948304 bytes: Success!

13338632 bytes read in 2161 ms (5.9 MiB/s)

98400 bytes read in 17 ms (5.5 MiB/s)

3653 bytes read in 1 ms (3.5 MiB/s)

3742 bytes read in 3 ms (1.2 MiB/s)

## Flattened Device Tree blob at 82000000

Booting using the fdt blob at 0x82000000

Loading Device Tree to 00000000fdda6000, end 00000000fdec1fff ... OK