Hi,

I had some problems in developing I2C.

The chip I used is TDA2SX, and the vsdk version is 03-06-00-00.

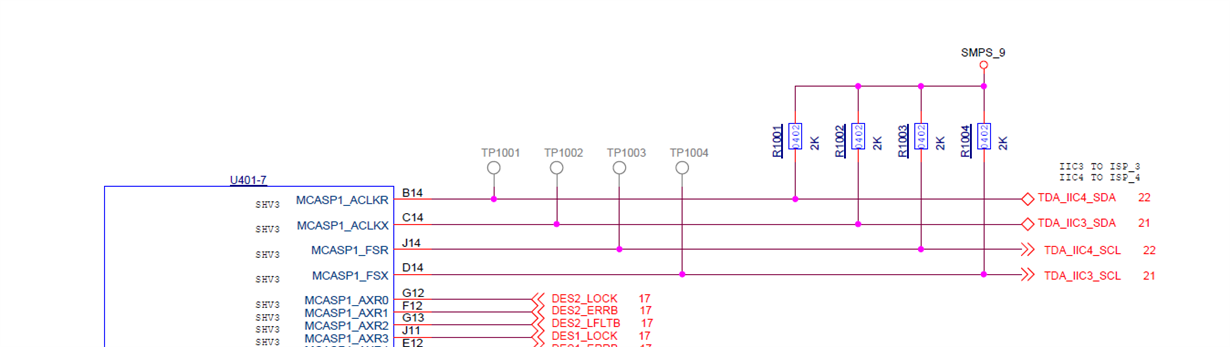

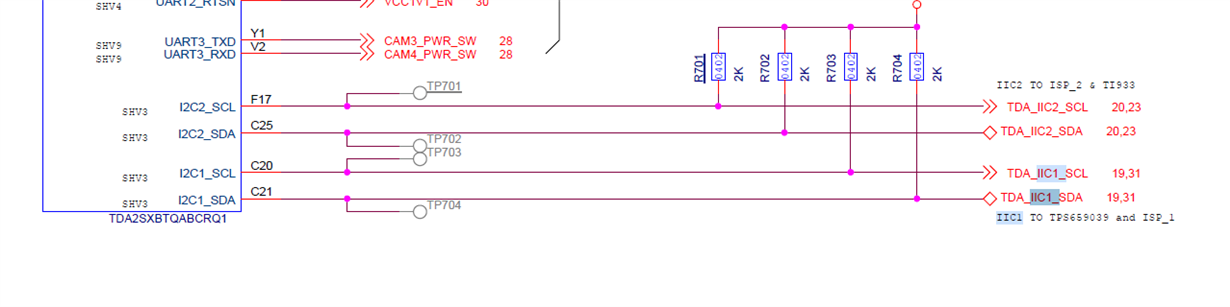

In our hardware design, four I2Cs were used to control four ISP processors, and the i2c hardware interface is as follows:

I had some problems in developing I2C.

The chip I used is TDA2SX, and the vsdk version is 03-06-00-00.

In our hardware design, four I2Cs were used to control four ISP processors, and the i2c hardware interface is as follows:

static Bsp_BoardI2cInstData gBoardTda2xxI2cInstData[] =

{

{

BSP_DEVICE_I2C_INST_ID_0, /* instId */

SOC_I2C1_BASE, /* baseAddr */

CSL_INTC_EVENTID_I2CINT1, /* intNum */

100U /* busClkKHz */

},

{

BSP_DEVICE_I2C_INST_ID_1, /* instId */

SOC_I2C2_BASE, /* baseAddr */

CSL_INTC_EVENTID_I2CINT2, /* intNum */

100U /* busClkKHz */

},

{

BSP_DEVICE_I2C_INST_ID_2, /* instId */

SOC_I2C3_BASE, /* baseAddr */

CSL_INTC_EVENTID_I2CINT3, /* intNum */

100U /* busClkKHz */

},

{

BSP_DEVICE_I2C_INST_ID_3, /* instId */

SOC_I2C4_BASE, /* baseAddr */

CSL_INTC_EVENTID_I2CINT4, /* intNum */

100U /* busClkKHz */

},

My test code for I2C is as follows:

static Int ReadIspReg0(UInt32 port_id)

{

Int32 retVal = BYD_DIAGNOSE_I2C_STATE_OK;

UInt32 slaveAddr = 0;

switch (port_id)

{

case 0:

slaveAddr = HSI2C_SLAVE_ADDR0;

Bsp_platformSetPinmuxRegs(

(UInt32) CTRL_CORE_PAD_I2C1_SDA_I2C1_SDA_MUXMODE_I2C1_SDA_0,

(UInt32) CTRL_CORE_PAD_I2C1_SDA,

BSP_PLATFORM_IOPAD_CFG_DEFAULT);

Bsp_platformSetPinmuxRegs(

(UInt32) CTRL_CORE_PAD_I2C1_SCL_I2C1_SCL_MUXMODE_I2C1_SCL_0,

(UInt32) CTRL_CORE_PAD_I2C1_SCL,

BSP_PLATFORM_IOPAD_CFG_DEFAULT);

break;

case 1:

slaveAddr = HSI2C_SLAVE_ADDR1;

Bsp_platformSetPinmuxRegs(

(UInt32) CTRL_CORE_PAD_I2C2_SDA_I2C2_SDA_MUXMODE_I2C2_SDA_0,

(UInt32) CTRL_CORE_PAD_I2C2_SDA,

BSP_PLATFORM_IOPAD_CFG_DEFAULT);

Bsp_platformSetPinmuxRegs(

(UInt32) CTRL_CORE_PAD_I2C2_SCL_I2C2_SCL_MUXMODE_I2C2_SCL_0,

(UInt32) CTRL_CORE_PAD_I2C2_SCL,

BSP_PLATFORM_IOPAD_CFG_DEFAULT);

break;

case 2:

slaveAddr = HSI2C_SLAVE_ADDR2;

Bsp_platformSetPinmuxRegs(

(UInt32) CTRL_CORE_PAD_MCASP1_FSX_MCASP1_FSX_MUXMODE_I2C3_SCL_10,

(UInt32) CTRL_CORE_PAD_MCASP1_FSX,

BSP_PLATFORM_IOPAD_CFG_INPUTENABLE_BI | BSP_PLATFORM_IOPAD_CFG_PULLTYPESELECT_UP);

Bsp_platformSetPinmuxRegs(

(UInt32) CTRL_CORE_PAD_MCASP1_ACLKX_MCASP1_ACLKX_MUXMODE_I2C3_SDA_10,

(UInt32) CTRL_CORE_PAD_MCASP1_ACLKX,

BSP_PLATFORM_IOPAD_CFG_INPUTENABLE_BI | BSP_PLATFORM_IOPAD_CFG_PULLTYPESELECT_UP);

break;

case 3:

slaveAddr = HSI2C_SLAVE_ADDR3;

Bsp_platformSetPinmuxRegs(

(UInt32) CTRL_CORE_PAD_MCASP1_FSR_MCASP1_FSR_MUXMODE_I2C4_SCL_10,

(UInt32) CTRL_CORE_PAD_MCASP1_FSR,

BSP_PLATFORM_IOPAD_CFG_INPUTENABLE_BI | BSP_PLATFORM_IOPAD_CFG_PULLTYPESELECT_UP);

Bsp_platformSetPinmuxRegs(

(UInt32) CTRL_CORE_PAD_MCASP1_ACLKR_MCASP1_ACLKR_MUXMODE_I2C4_SDA_10,

(UInt32) CTRL_CORE_PAD_MCASP1_ACLKR,

BSP_PLATFORM_IOPAD_CFG_INPUTENABLE_BI | BSP_PLATFORM_IOPAD_CFG_PULLTYPESELECT_UP);

break;

default:

break;

}

Vps_printf("begin read i2c\n");

UInt8 sendData[3] = {0x00, 0x00, 0x03};

UInt8 recvData[2] = {0xff, 0xff};

Vps_printf("portid is %d\n", port_id);

Bsp_deviceRead8(port_id,

slaveAddr,

sendData,

recvData,

1);

Vps_printf("recv data is 0x%x, 0x%x\n", recvData[0], recvData[1]);

return retVal;

}

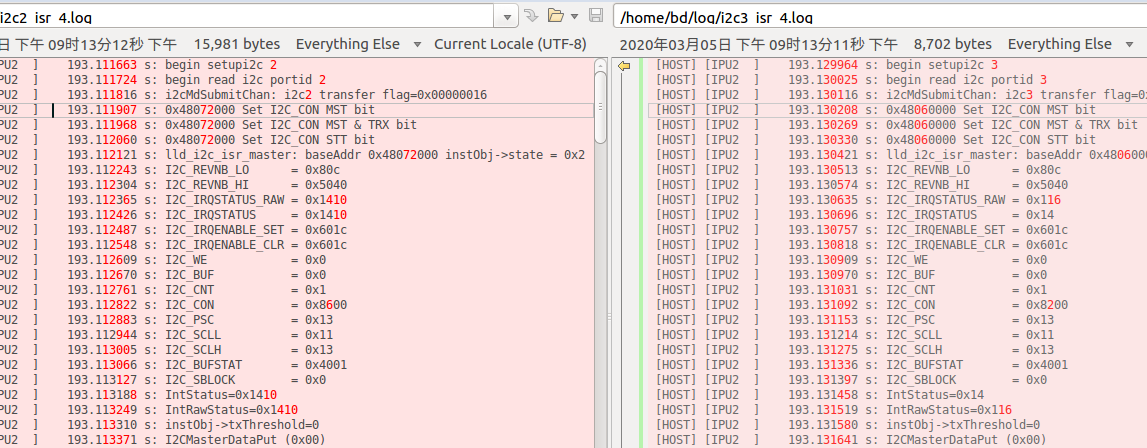

The test results for the 4 i2c buses are as follows, and you can see that both i2c0 and i2c1 were read successfully and the returned data was correct, but the i2c2 and i2c3 reads failed. Where i2c2 has an error state of LLD_HSI2C_NACK_ERR, i2c3 has an error state of LLD_HSI2C_ETIMEOUT.

[HOST] [IPU2 ] 54.619288 s: portid is 0 [HOST] [IPU2 ] 54.619593 s: recv data is 0xda, 0xff [HOST] [IPU2 ] 54.619654 s: SetupI2C ok [HOST] [IPU2 ] 54.619715 s: begine setupi2c 1 [HOST] [IPU2 ] 54.619776 s: begin read i2c [HOST] [IPU2 ] 54.619837 s: portid is 1 [HOST] [IPU2 ] 54.620447 s: recv data is 0xda, 0xff [HOST] [IPU2 ] 54.620569 s: SetupI2C ok [HOST] [IPU2 ] 54.620630 s: begine setupi2c 2 [HOST] [IPU2 ] 54.620661 s: begin read i2c [HOST] [IPU2 ] 54.620722 s: portid is 2 [HOST] [IPU2 ] 54.621149 s: src/bsp_deviceI2c.c @ Line 335: [HOST] [IPU2 ] 54.621271 s: Write bus error begin,I2C2: DEV 0x6d: RD 0x00 ... ERROR !!! [HOST] [IPU2 ] 54.621362 s: src/bsp_deviceI2c.c @ Line 362: [HOST] [IPU2 ] 54.621454 s: error code -21: DEV 0x6d: RD 0x00 ... ERROR !!! [HOST] [IPU2 ] 54.621606 s: src/bsp_deviceI2c.c @ Line 428: [HOST] [IPU2 ] 54.621667 s: I2C2: Error timeout 1 ms!!! [HOST] [IPU2 ] 54.621759 s: recv data is 0xff, 0xff [HOST] [IPU2 ] 54.621820 s: SetupI2C ok [HOST] [IPU2 ] 54.621850 s: begine setupi2c 3 [HOST] [IPU2 ] 54.621911 s: begin read i2c [HOST] [IPU2 ] 54.621972 s: portid is 3 [HOST] [IPU2 ] 59.621881 s: src/bsp_deviceI2c.c @ Line 335: [HOST] [IPU2 ] 59.621972 s: Write bus error begin,I2C3: DEV 0x6d: RD 0x00 ... ERROR !!! [HOST] [IPU2 ] 59.623375 s: src/bsp_deviceI2c.c @ Line 344: [HOST] [IPU2 ] 59.623497 s: Write Time out,I2C3: DEV 0x6d: RD 0x00 ... ERROR !!! [HOST] [IPU2 ] 59.623589 s: src/bsp_deviceI2c.c @ Line 362: [HOST] [IPU2 ] 59.623894 s: error code -2: DEV 0x6d: RD 0x00 ... ERROR !!! [HOST] [IPU2 ] 59.624016 s: src/bsp_deviceI2c.c @ Line 428: [HOST] [IPU2 ] 59.624077 s: I2C3: Error timeout 5002 ms!!! [HOST] [IPU2 ] 59.624168 s: recv data is 0xff, 0xff

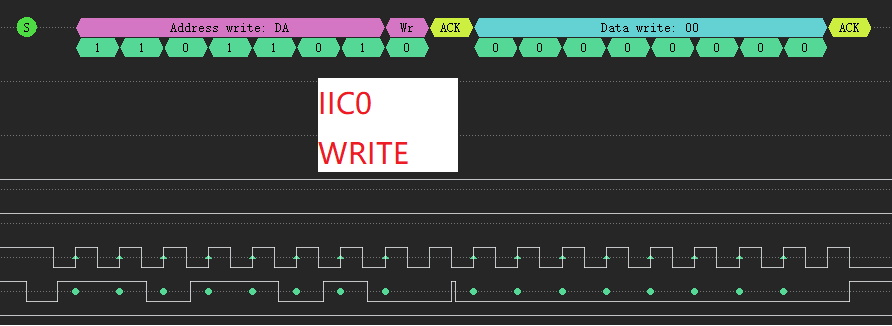

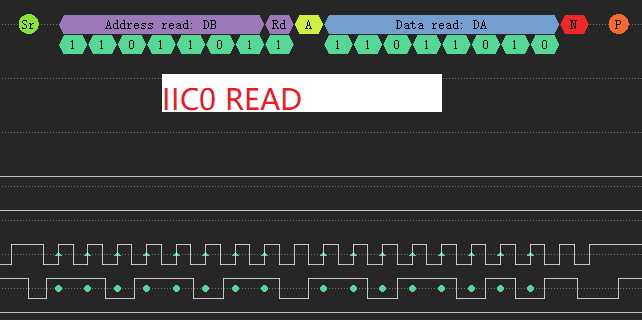

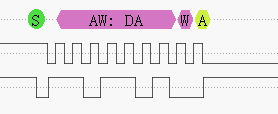

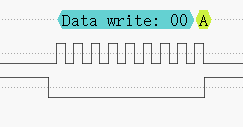

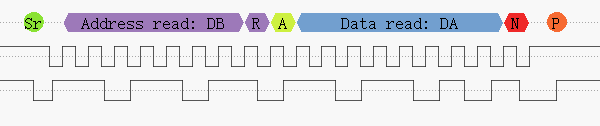

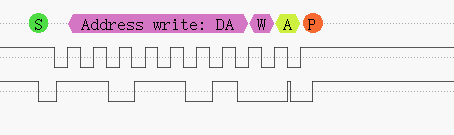

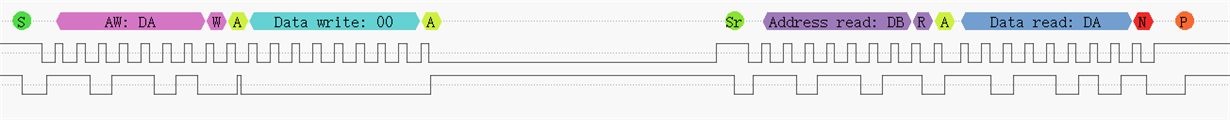

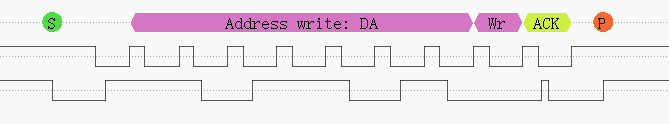

I monitored the i2c signal on the bus, where i2c0 and i2c1 write and read the signal as follows:

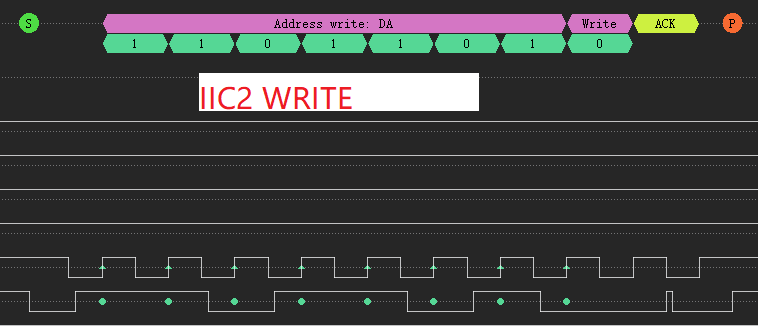

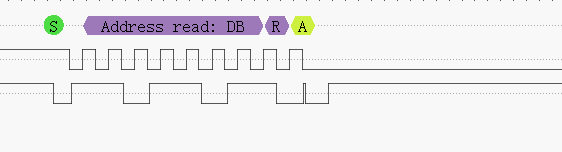

i2c2 and i2c3 have an error in the write register address, but from the signal point of view, after master write register address, slave has sent a ack signal, but why i2c2 will have LLD_HSI2C_NACK_ERR error?