Hi champs,

customer need to know if he can change individual "dual channels" A vs B.

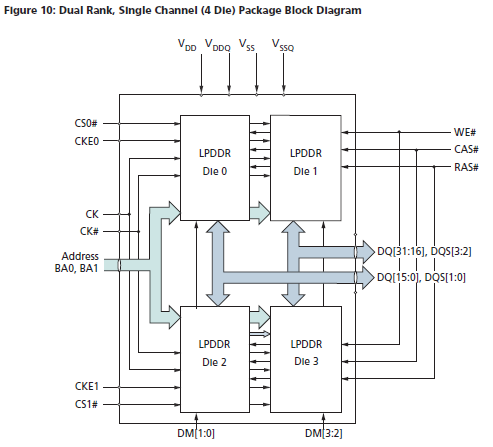

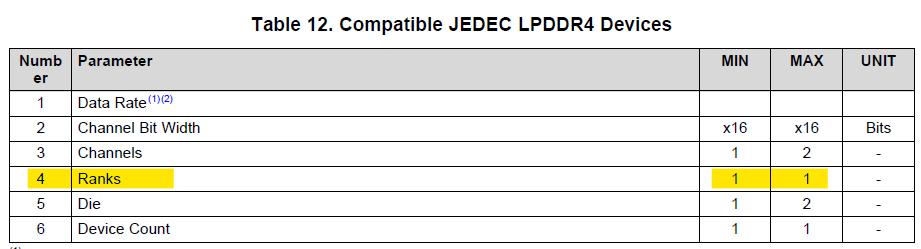

Idea is 2x16bit Dual Rank System

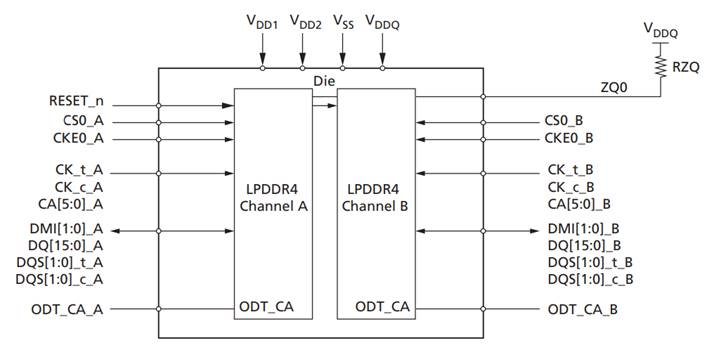

Channel A = 16bit

Channel B = 16bit

each channel has its own address/control signals.

He wants to connect to two LPDDR4 memories in this way:

Memory IC1 2x16bit Bus

Channel-A -> Memory IC1.Channel-A und IC1.ChipSelect0 A zu A routing

Channel-B -> Memory IC1.Channel-B und IC1.ChipSelect0 B zu B routing

Memory IC2 2x16bit Bus

Channel-A -> Memory IC2.Channel-B und IC1.ChipSelect1 A zu B routing

Channel-B -> Memory IC2.Channel-A und IC1.ChipSelect1 B zu A routing

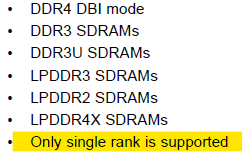

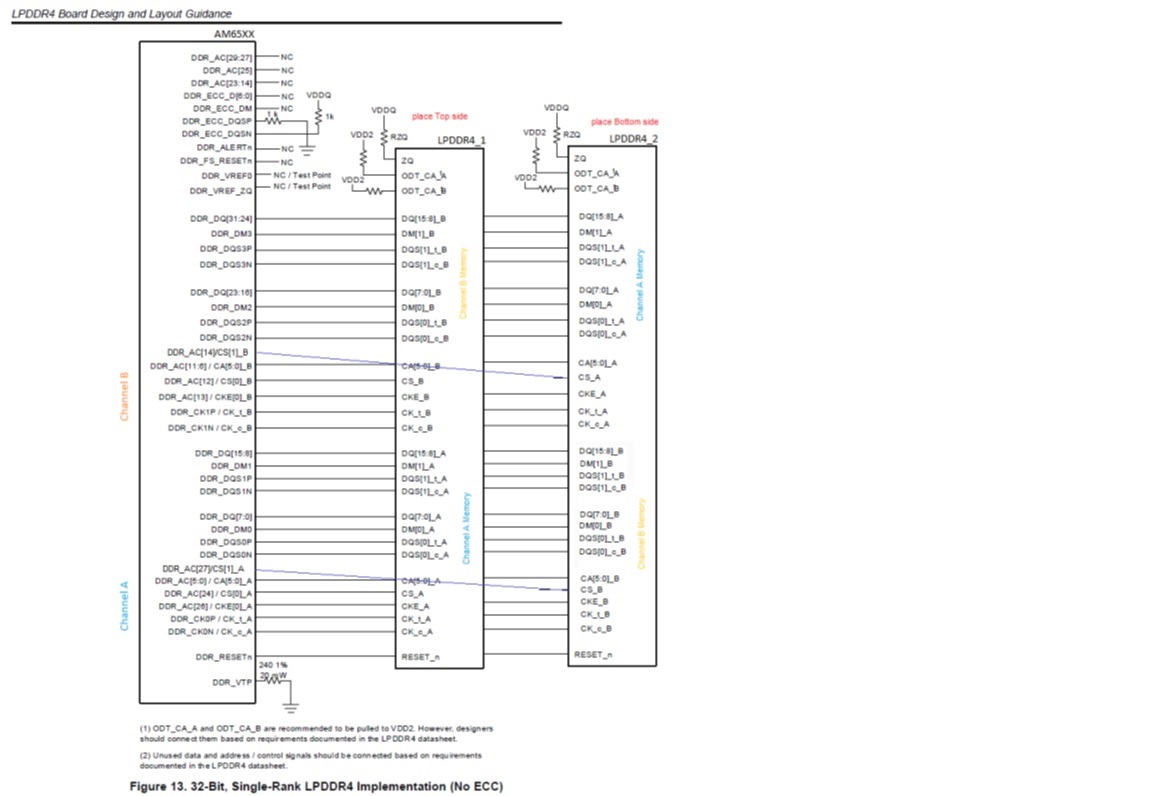

According to layout recommendation from TI this seems not to work:

Channel, Byte, and Bit Swapping

All signals, including data and address/control, must be routed 1 to 1 from the DDR controller to the LPDDR4 memory.

Byte swapping across channels or within a channel is not allowed.

Similarly, data bit swapping across byte lanes or within a byte is also not allowed.

In addition, byte lanes 0 and 1 of the DDR controller must be routed to channel A of the LPDDR4 memory,

and byte lanes 2 and 3 of the DDR controller must be routed to channel B of the LPDDR4 memory.

Q: What is background of this statement ? Any ways to realize customers ideas ?