Other Parts Discussed in Thread: AM3352,

Dear Champs,

I'm investigating an issue with the AM3352 LCD controller that's related to the timing between HSYNC and VSYNC.

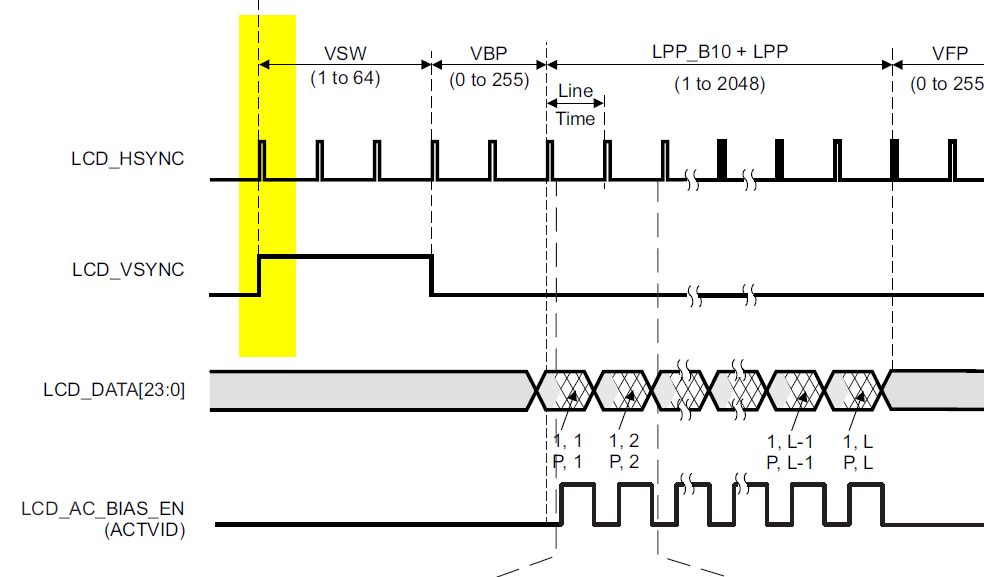

I'm looking at the AM3358 datasheet timing for the LCD controller in raster mode. Figures 7-82 and 7-83 are drawn such that they give the impression that the rising edge and falling edge of VSYNC are aligned with the rising edge of HSYNC.

Here's a screenshot of figure 7-82 that shows this.

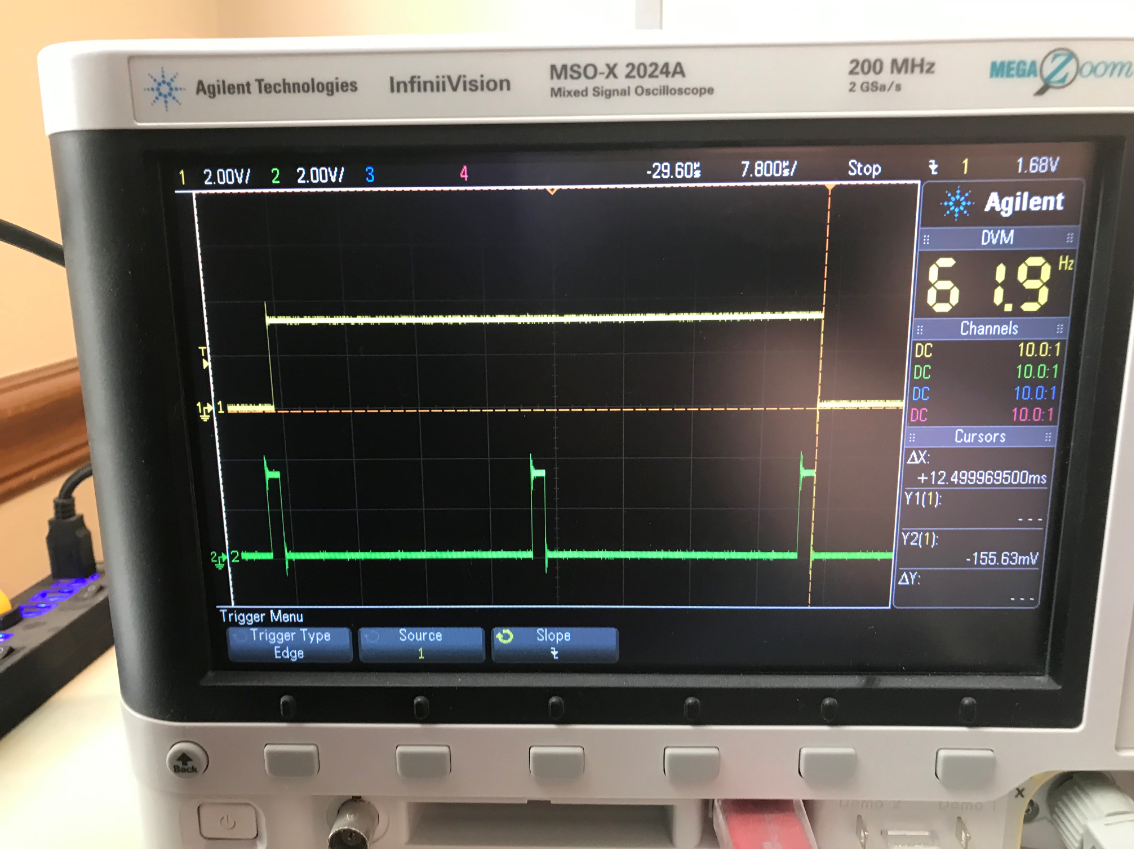

However, what's been observed is that the edges of VSYNC are aligned with the falling edge of HSYNC. To verify this, I measured the signals on our AM335x GP EVM. Sure enough, the VSYNC edges align with the falling edges of HSYNC.

Scope capture of HSYNC(green) and VSYNC(yellow) on AM335x GP EVM

Is there a way to have the rising edge of HSYNC line up with the rising edge of VSYNC?