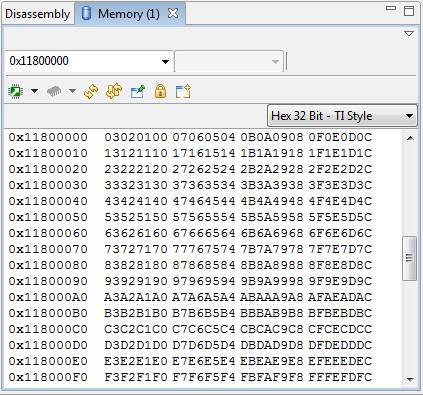

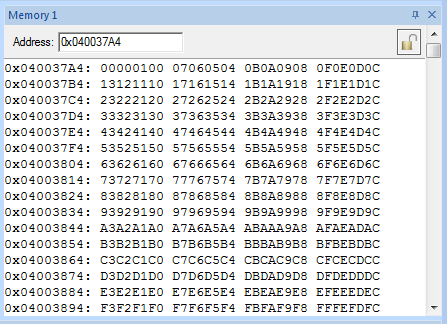

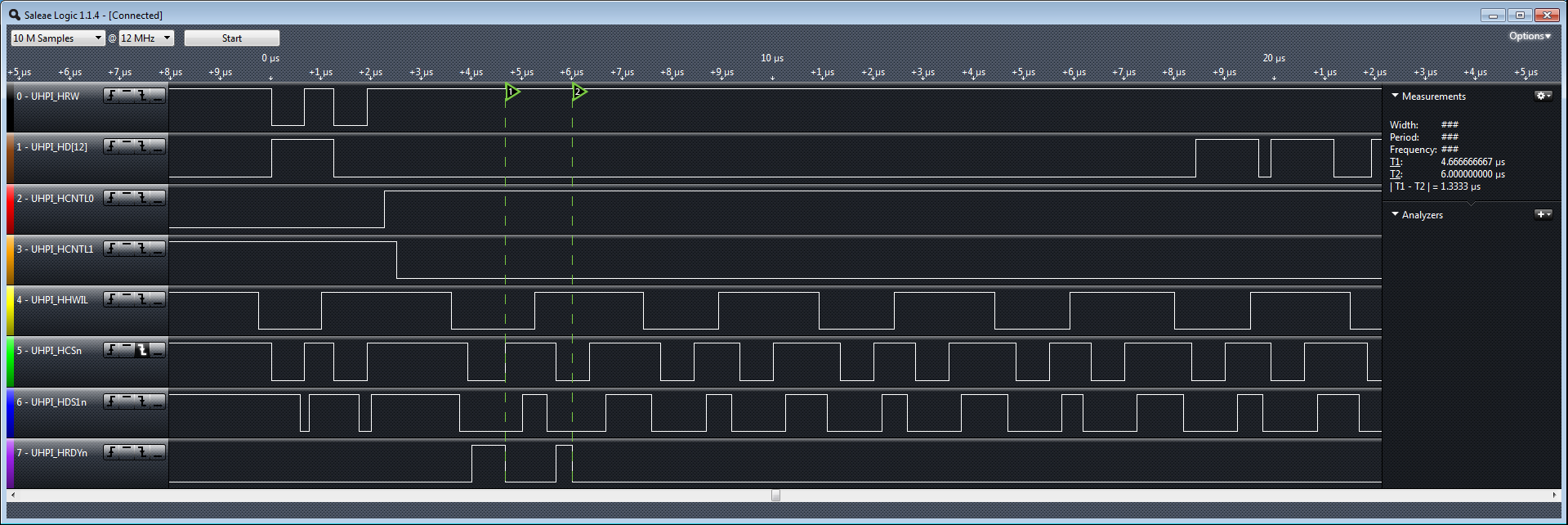

I'd like to continue with OMAP137 HPI boot problem discussion in another post due to its 3-page length. The point is when I read back the written section on C6747 from host in order to perform CRC computation, the first 2-bytes are always zero. Brad Griffis suggested that it could be a FIFO issue but I've tried to flush it by previous readings with no success. On the other hand, while my C6747 application runs, read HPI transfers are ok. In short, I don't know why HPI works that way during boot. Any ideas?

I could workaround this problem by reading previous 4-bytes of every section. I've tried it and works fine but I think it isn't a neat solution. Sometimes this kind of workarounds could mask another problem.

Regards,

Gaston