Other Parts Discussed in Thread: STRIKE

I am testing the BIOS PSP GPIO example code and somehow I cannot set it up to generate an interrupt on GPIO falling edge. The example code is installed at the default directory:

C:\Program Files\Texas Instruments\pspdrivers_01_20_00\packages\ti\pspiom\examples\evmOMAPL137\gpio\src\gpioSample_io.c

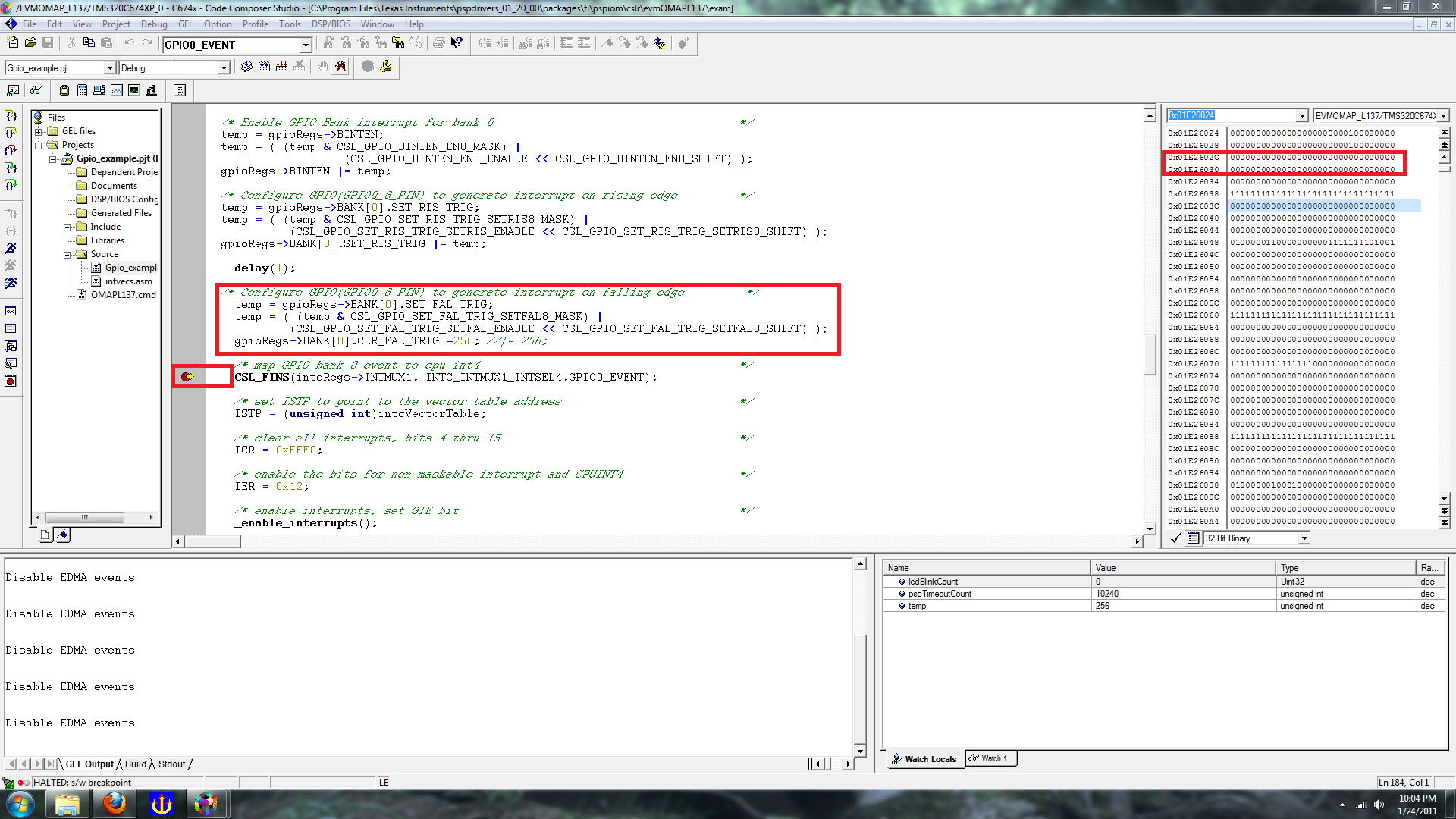

The original code will generate an interrupt at rising edge (SW3-1 from 8 to 1) and it works as expected. However, after I changed it to generate an interrupt on falling edge, it didn't work that way and still can only generates an interrupt on rising edge. Does anybody have suggestions what I may have done wrong? Thank you!

The following is what I modified to the original code:

/* Enable GPIO Bank interrupt for bank GPIO_BANK_0 */

Gpio_bankInterruptEnable(gpio0,GPIO_BANK_0);

/* Configure GPIO(GPIO0_8_PIN) to generate interrupt on rising edge */

//Gpio_setRisingEdgeTrigger(gpio0,GPIO0_8_PIN); Line 118, original code

Gpio_setFallingEdgeTrigger(gpio0,GPIO0_8_PIN); Line119, new code

/* Set the interrupt handler for GPIO0_8_PIN. However we cannot register

* interrupts for individual pins in OMAPL137, therefore register interrupt

* for the associated bank(BANK0) as a whole

*/

UserIntrCmdArg.value = GPIO_BANK_0;