Part Number: AM4376

Hello Forum,

we are using a MICRON DDR3L MT41K64M16TW-107 IT together with the AM4376. In an earlier project, the EMIF Tool was not yet available. At this time i was using the AM43xx DDR3 Timing Configuration Tool which was an EXCEL spreadsheet as well.

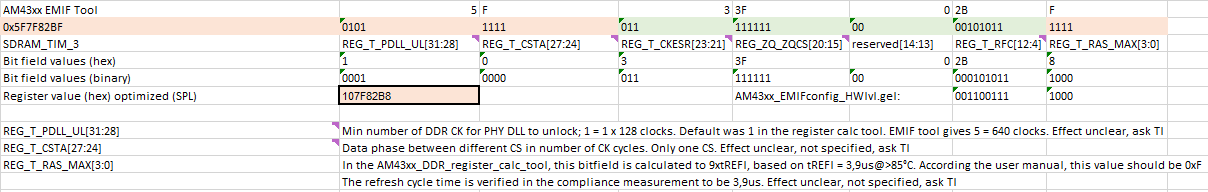

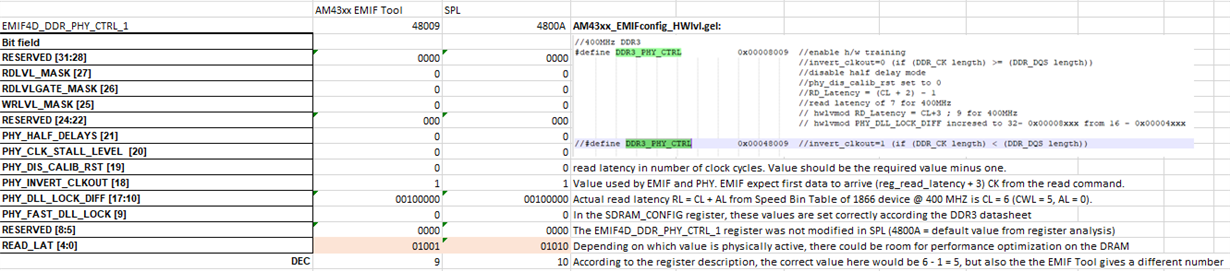

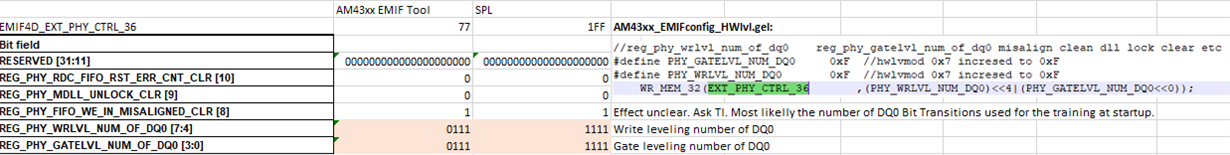

With a new project, I started to use the AM43xx EMIF Tool V21 to setup up the configuation register values and to review the values I derived in the earlier project. Especially in Step 2 where i need to enter timing values from the part datasheet, some fields are turning red because of deviations from the JEDEC bitfield values assuming a DDR3-800@400MHz. I also get differences in some of the bitfields I deternined earlier with the AM43xx DDR3 Timing Configuration Tool.

The earlier desig is working very stable on the DRAM over temperature since 2015, after we fixed some trouble with the HW leveling. But probably there is some room for optimization here as well.

The part we are using is from speed grade DD3L-1866 and we are operating at 400MHz. Currently I entered the timing specifications for this specific device/speed grade (1866), but because of the red fields and the differences I get, I am not sure anymore about what to enter.

Here my questions:

Do i need to enter the values for a speed grade 800 device, even we are using a speed grade 1866 device?

Or do I need to enter the timing values for 1866?

The user guide for the tool doesn't answer this question.

Thank you very much in advance for your support.

Best regards

Ralph