Part Number: TDA4VMXEVM

Hi, we are analyzing Ethernet capabilities on TDA4x with goal of using it for development of TDA4 SoC based platform.

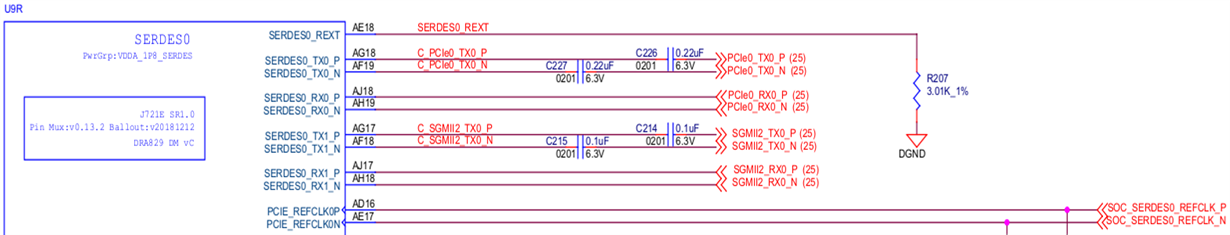

We can see that TDA4VM EVM evaluation module have Quad Ethernet expansion board with integrated Quad-SGMII PHY and two Stacked RJ45 SGMII interfaces.

When we boot linux none of these interfaces can be found by kernel, unlike MCU RGMII interface which is named eth0 by kernel, see ifconfig result below:

eth0 Link encap:Ethernet HWaddr F4:84:4C:F4:D7:FF

UP BROADCAST MULTICAST MTU:1500 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

We cannot figure out why we cannot see these four interfaces on Quad Ethernet expansion board connected to MAIN domain via SERDES0?

And how can linux know of MCU RGMII interface when it is connected to the MCU domain and not MAIN domain?

Can you help us to better understand how to manage these interfaces from linux side?

Regards.

Uros