According to EMIF user guide (chapter 6), the turnaround time for back to back sync read is 0, 0 for back to back sync write, and 1 for sync write followed by sync read.

Sync EMIF timing that I captured didn't follow the user guide. Any idea why?

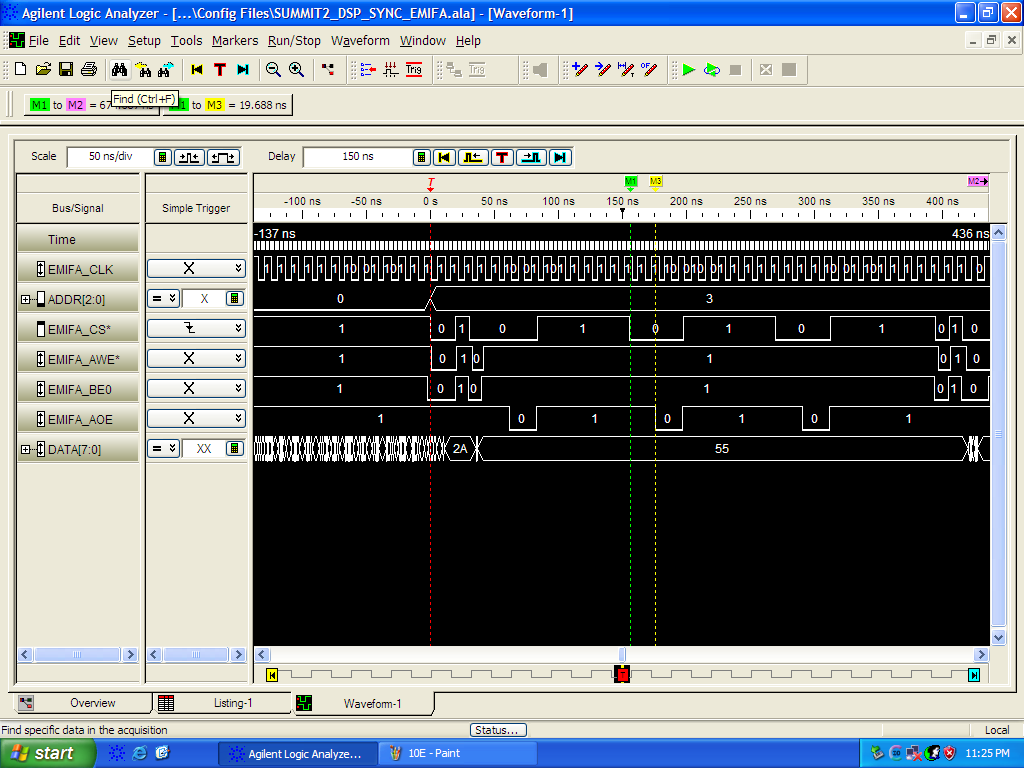

My CEnCFG setting is 0x8000020e (R_LTNCY = 3, W_LTNCY = 0, CS goes active until SOE goes inactive)

Attached is my captured sync EMIF signals. I did 3 back to back sync writes, followed by 3 back to back sync reads.

- There are 7 clock cycles in between back to back sync read.

- There is 0 clock cycle in between sync write and sync read

- There is 1 clock cycle in between back to back sync write

Thanks.