The NAND memory space could be accessed by CS3 of TMS320C6748 is only 32MB x 8 = 256Mbit wide.

I only want to use one single NAND with 2Gbit memory space.

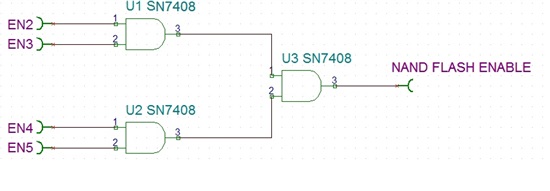

How I can use other chip enable pins such as CS2, CS4 and CS5 to access the rest memory space of 2G bit NAND flash?

I want to use a CPLD to interface between TMS320C6748 and NAND, but I am afraid the timing will be bad.

Please help.

Thanks in advance.