Part Number: AM6548

Dear TI team,

I'm trying to synchronize our AM65x operating as an PCIe EP connected to a x86 processor via PCIe PTM.

Synchronizing the PTM local clock apparently "simply works" after enabling PTM in the PCIe register space, i.e. the PTM_REQ_CONTEXT_VALID register gets set, and I can see the PCIE_EP_PTM_REQ_LOCAL_LSB_OFF/...MSB_OFF being set to something that matches the current PTM time from the x86.

My issue is that I haven't yet found a reliable way of using the PTM local clock to synchronize other clocks within the AM65x from there. The main issue that I'm seeing is that the PTM clock update is not synchronized with CPTS module. IF the PTM local clock is not frequency adjusted to the PTM master, the PTM local clock is going to drift from the master clock. This means I'd have to make sure that the PTM local clock was recently updated, but for lower-order bits of PTM local clock it becomes difficult/impossible to tell what the PTM local clock time was that triggered a CPTS hardware push event. For higher-order bits of PTM local clock it's of course easier to tell what the PTM local clock time was at the time of the hardware push event, but the last PTM update could be seveal milliseconds old, and the clocks would have drifted.

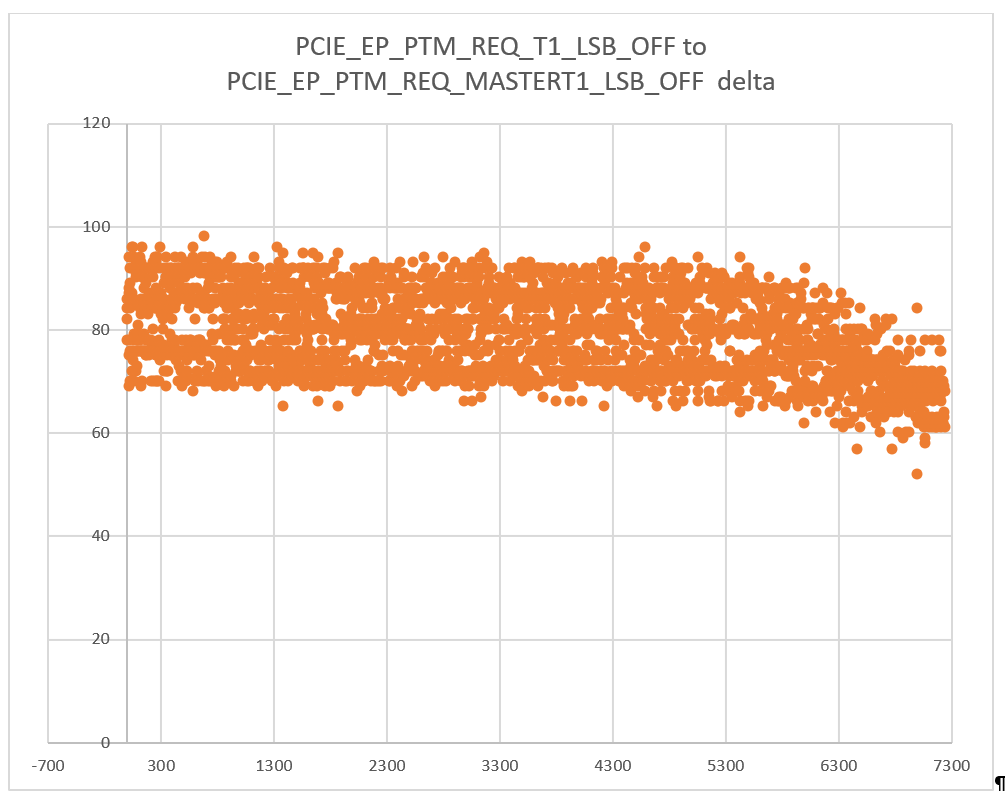

I'm assuming that the PTM local clock is not frequency adjusted to the synchronized master clock. In my current tests I'm seeing ~80ns difference between succsessive context updates (PTM_CLK_UPDATED interrupts) in the PCIE_EP_PTM_REQ_T1_LSB_OFF and PCIE_EP_PTM_REQ_MASTERT1_LSB_OFF registers.

- Is it safe to assume that PCIE_EP_PTM_REQ_T1 vs. PCIE_EP_PTM_REQ_MASTERT1 shows the difference between PTM local clock and the PTM master clock at the time the PTM requester initiated the last update?

- Is it safe to assume that PTM local clock got stepped to match the PTM master clock right before the PTM_CLK_UPDATED clock got signaled?

- Is my assumption correct that the PTM local clock is not frequency adjusted to match the master clock?

- Which clock signal is used to drive the PTM local clock?

Any guidance on how to use the PCIe PTM/CPTS functionality would be highly appreciated.

Regards,

Dominic