TI experts,

I have a custom board with Sitara AM6548 where the clocking schema is identical to the IDK board.

We use SYS/BIOS, CCS9.2 and currently processor_sdk_rtos_am65xx_6_01

We run our own PRU program (quite simple one, already stripped down for bug analysis).

When running PRU0 of ICSSG2, I configured CORE_CLK = 200 MHz using the 2 registers described in the TRM:

200 MHz

– CTRLMMR_ICSSGn_CLKSEL[0] CORE_CLKSEL = 1 (CPSWHSDIV_CLKOUT2 is source clock)

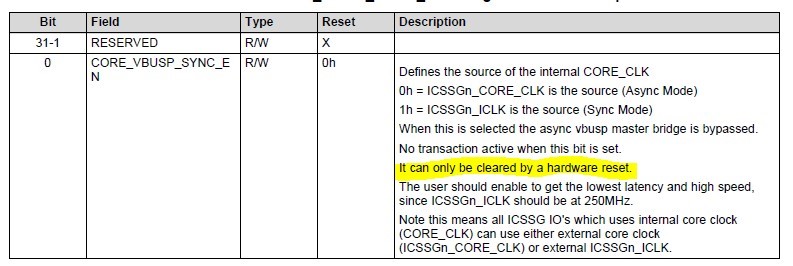

– ICSSG_CORE_SYNC_REG[0] CORE_VBUSP_SYNC_EN = 0 (Async Mode, default)

The ICSSG2 PRU program is loaded via the A53 core.

The A53 program contains the PRU program as binary and loads it to ICSSG2.

When I load the A53 program via CCS/JTAG the behavior of the PRU is correct.

But when I boot it from sd-card, the PRU runs with 250MHz instead of 200MHz!

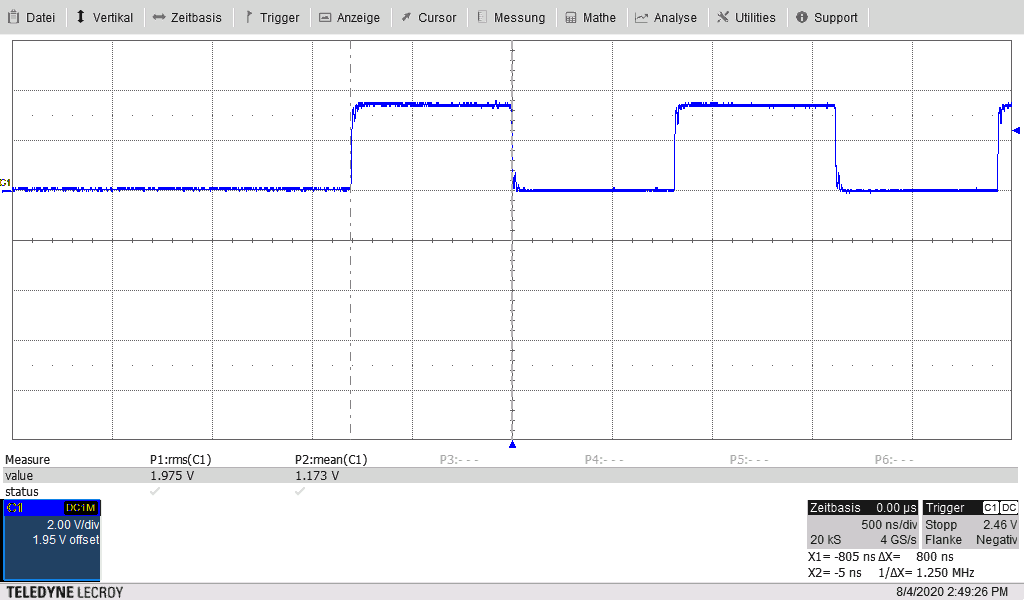

To prove this I have the following PRU code (I did also other measurements, all say the same):

__R30 |= (1 << PRU_PIN_SYNC); // high

__delay_cycles(200); // 200 MHz: 200*5ns = 1000ns = 1us

// 250 MHz: 200*4ns = 800ns = 0.8us

__R30 &= ~(1 << PRU_PIN_SYNC); // low

__delay_cycles(200);

On the oscilloscope I see pulses of exactly 1000ns when loading via JTAG and 800ns when booting from sdcard.

I double checked the 2 registers by reading them after startup:

Via UART_printf()

a53>fsitest FsiTest: initialize PRUs CFG0_ICSSG2_CLKSEL: 1 ICSSG2_CORE_SYNC_REG: 0

and also via our UART mem dump

a53>mem dump32 0x108048 1 0x00108048: 00000001 a53>mem dump32 0xB22603C 1 0x0B22603C: 00000000

What could be the reason for this too fast PRU CORE_CLK even if the configuration registers are correct?

Best regards,

Ruediger Wurth