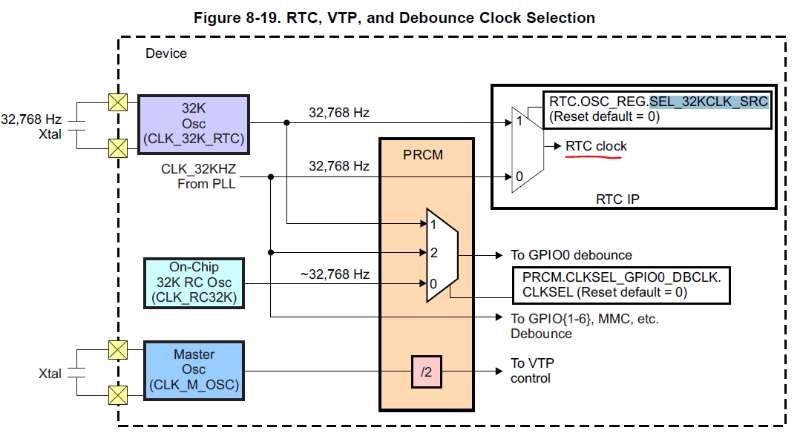

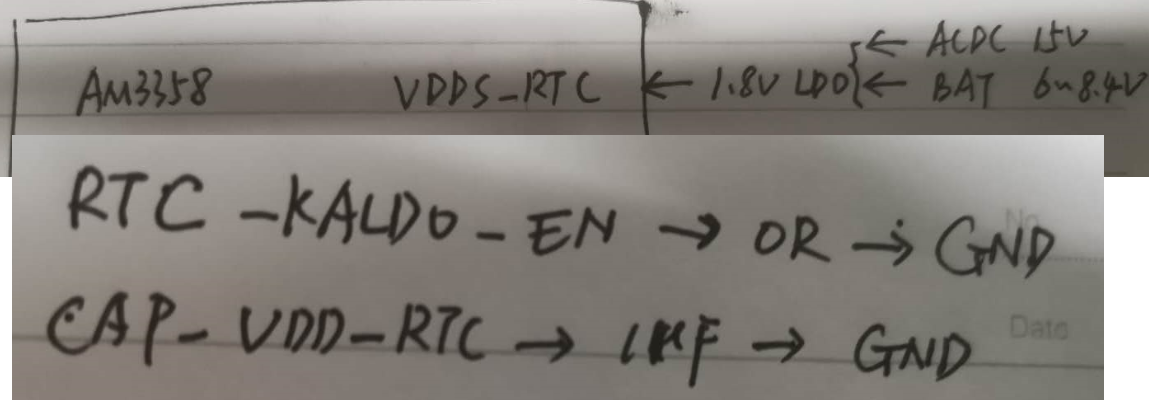

Customer uses CLK_32KHz from PLL for RTC, but find the RTC time is not accuracy, some board count ahead, some boards count behind, from TRM, the divider would provide a accurate 32.768KHz clock, so the RTC time should also be accurate. Is it the nature of counting RTC with the clock from PLL? or something else?

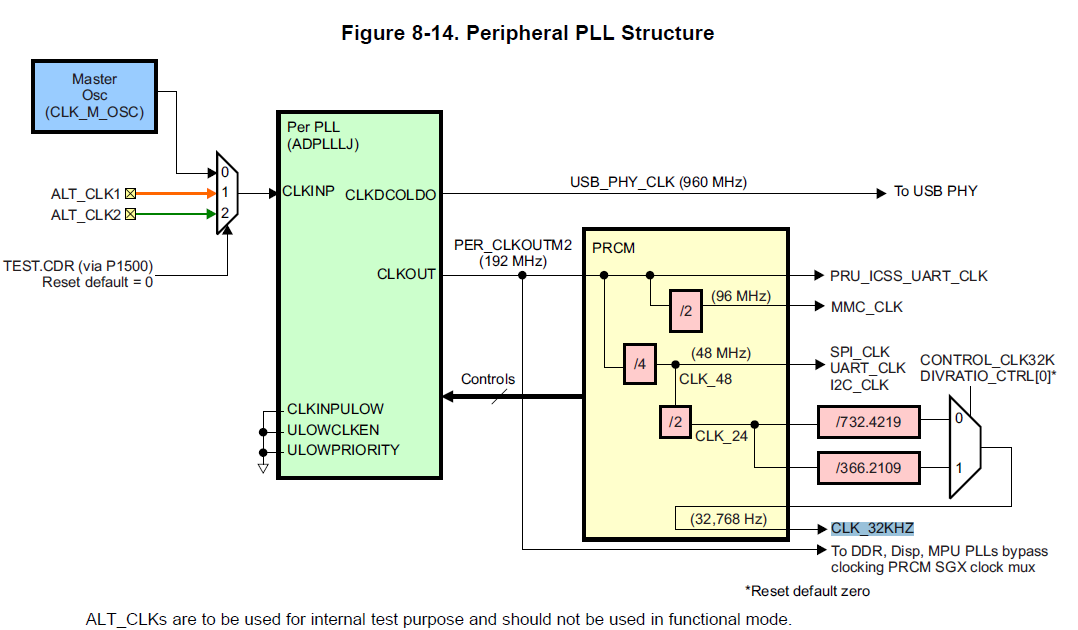

The 48-MHz clock is further divided by a fixed /2

divider and a fixed /732.4219 divider to create an accurate 32.768-KHz clock for Timer and debounce use.