I am using the 5509A and configuring Timer0 to be an external clock input. I have used the CSL to set up the timer.

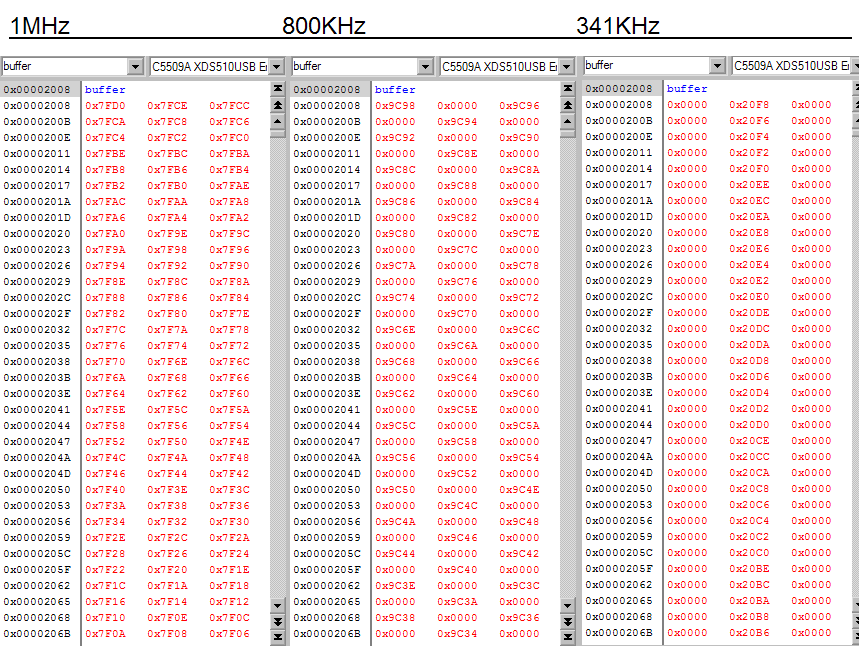

For frequencies above 1MHz, the TIM0 and PSC tick appropriately. When the frequency is at about 1MHz or below, the TIM0 does not tick properly. It appears to be ticking too fast; I assume it is a corruption of some sort.

The clock signal going in is very clean.

Any ideas? I have improved the performance by inserting a delay between stopping the timer and reading the TIM0 and PSC values.