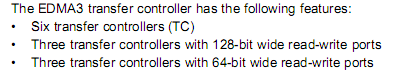

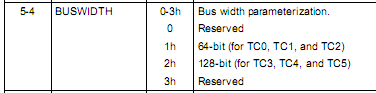

On page 68 of the manual in table 2-18 a listing is shown of the available TCs on the C6474 and according to the table they are all identical in specs. However, in SPRAAW5 (C6474 Module Throughput) on page 5, Figure 5, the EDMA TCs are split in 2 groups of 3: one group connected to the SCR A with a 128-bit wide bus and one group to SCR B with a 64-bit wide bus. On page 8, section 4.2 this is elaborated on.

My guess is that the "C6474 Module Throughput" document is correct, can somebody confirm?

Also, is the C6474 completely identical to the TCI6488?

Thanks,

-Dirk