Hi All,

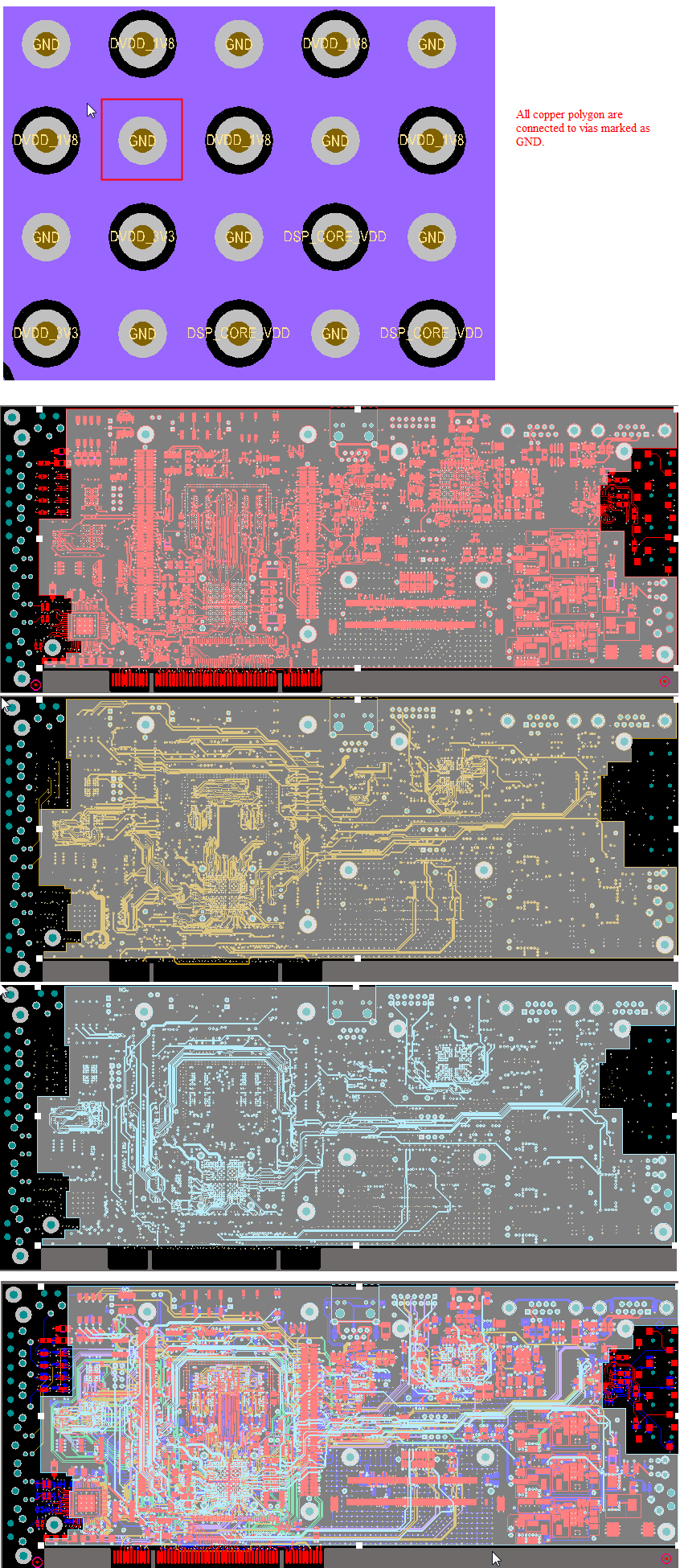

I have found that with the EVM6437 board which I am studying, in all layers there are large area of polygons which has areas dozens of times to that of tracks.

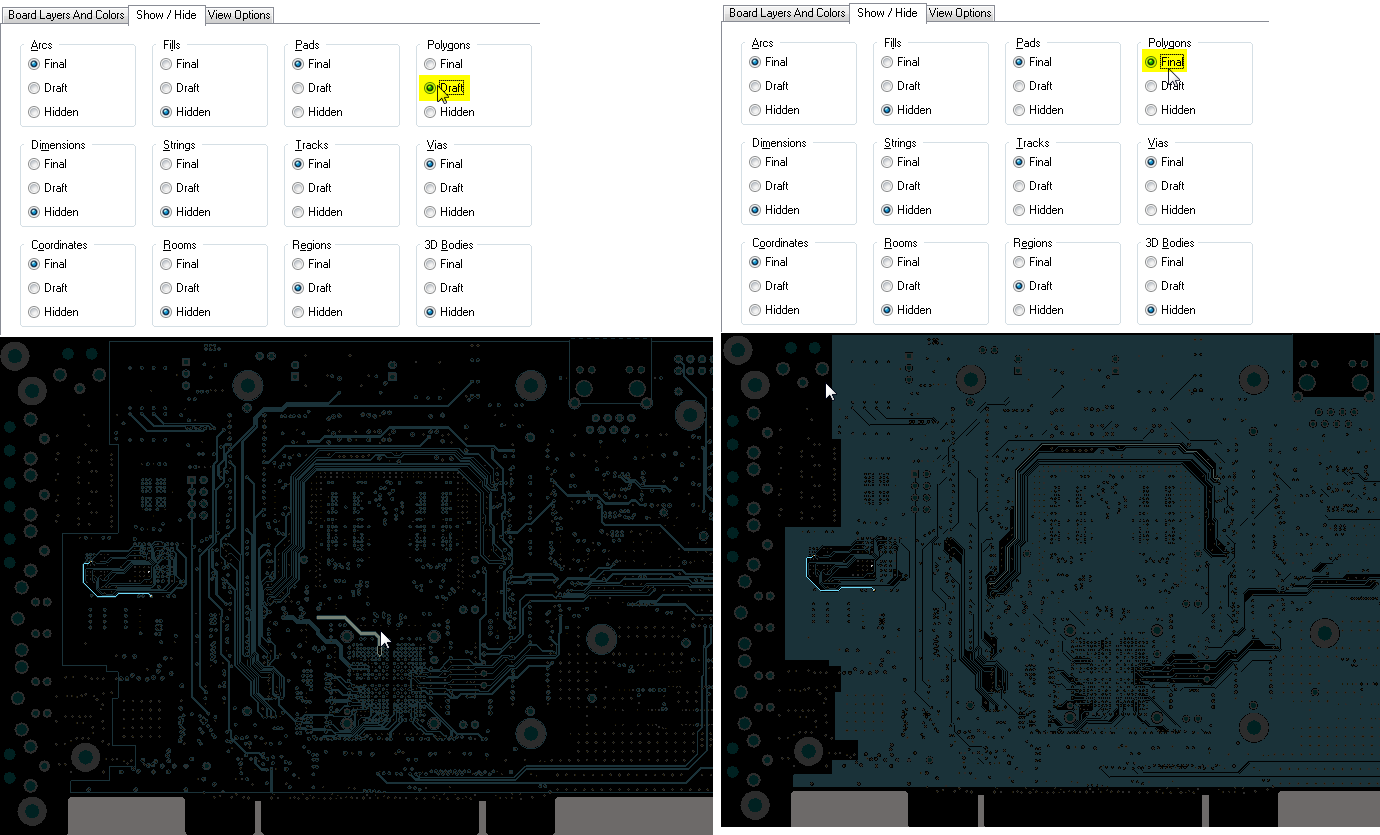

The attached picture show a comparison on Mid-layer 2 when Polygon display is switched between "draft" and "final", and the difference is clear.

I searched and read some articles on the Internet about polygon areas in PCB, but still haven't understood it well.

Isn't that tracks themselves alone are sufficient for carrying signals? Some large areas of copper might be useful on power or ground planes, as well as for EM shielding. However, why on all SIGNAL layers do there exist such large areas of polygon (copper?), which gives the impression that they are primary and the tracks are secondary?

My view is that if tracks are needed, some small portion would be enough, and they ought to be mostly on power/ground planes. But why there are so much of them, to the extent that they are the predominant, on all signal layers of the board?

Hope someone could help with this.

Zheng