Dear experts,

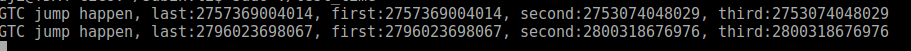

Our customer is seeing that reading GTC from A72 will has following issue:

When LO overflows, HI should increase by 1. But they find that, LO overflows, but HI is not increased.

Do you have any suggested best practice to read these 2 32bit registers?

Thanks & Best Regards!

ZM