Other Parts Discussed in Thread: SYSBIOS

Tool/software: TI C/C++ Compiler

Hello Experts,

If I could be pointed in the correct direction, please.

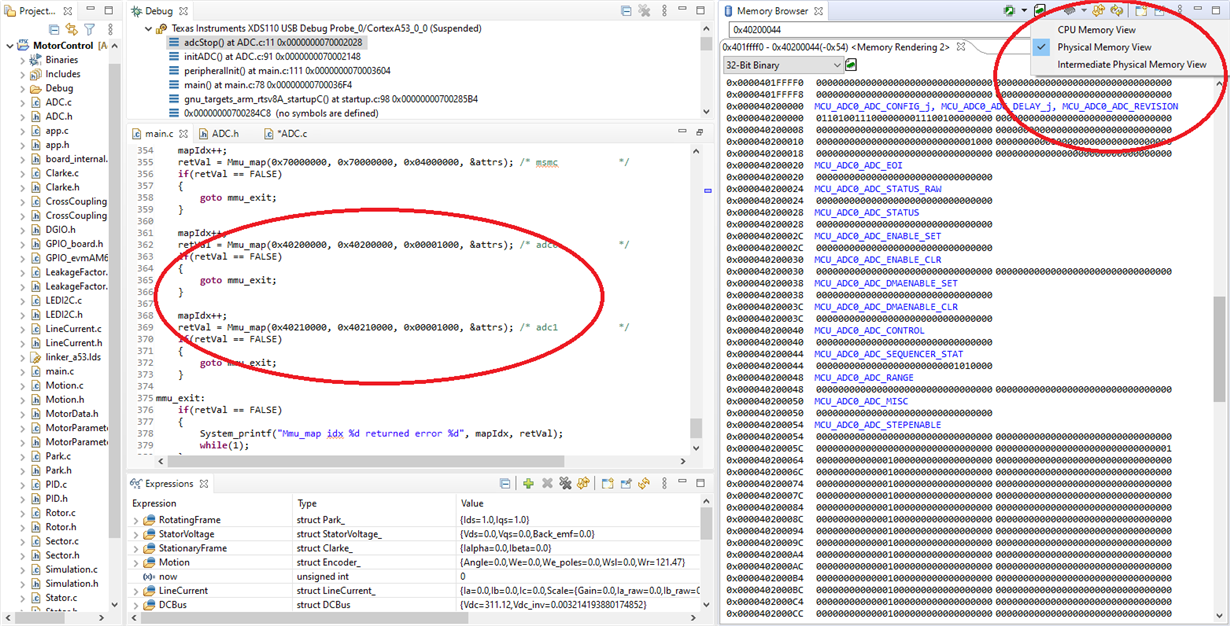

The below image is a screenshot of CCS. The top right red oval indicates a drop-down menu.

Question:

What is this?. What memory is this being associated with?

I have also indicated another oval to the bottom left, this is the RTOS "mapping".

At the risk of sounding completely daft, I'm assuming these drop-downs are related to virtual memory.

Question: If this is the case? Then where is the intermediate memory viewed from? What is this drop-down menu indicating/doing?.

Is this implying that the interconnect communication is implicitly happening by virtue that I have set up the RTOS function "Mmu_map" or do I need to set this up?

I am "writing" values to the ADC registers, but I am not completely convinced that I am. Sometimes I see it in CPU memory other times in physical memory, especially when single-stepping the software.

Thanks

Carl