Other Parts Discussed in Thread: OMAPL138

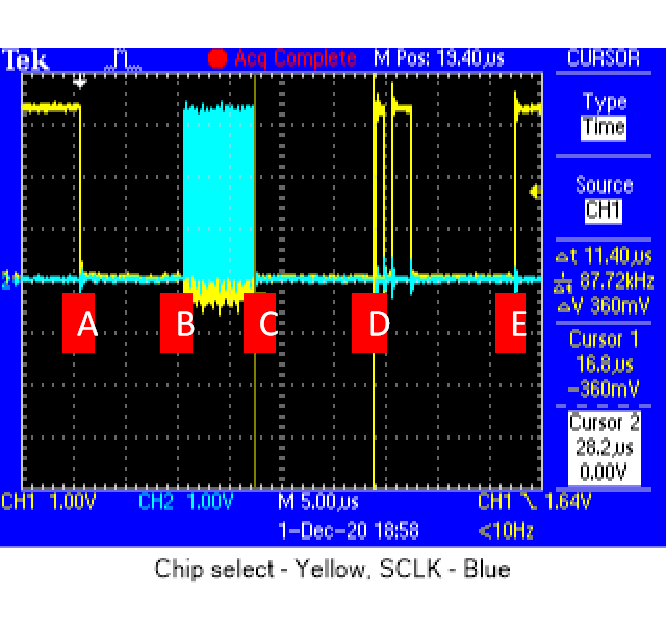

I am trying to use DMA for SPI in C6748 DSP. Using DMA would add an additional time after CS (around 8 us) and 21 us at the end of SPI transaction

SDK used : processor_sdk_rtos_omapl138_6_03_00_106

I found a related issue in https://e2e.ti.com/support/legacy_forums/embedded/tirtos/f/355/t/98047?SPI-DMA-timing

But rebuilding the EDMA drivers as suggested in the thread doesnot help.

Could you please let me know what could be the possible reason for this additional time and how to remove this?