Other Parts Discussed in Thread: SYSBIOS,

Hello,

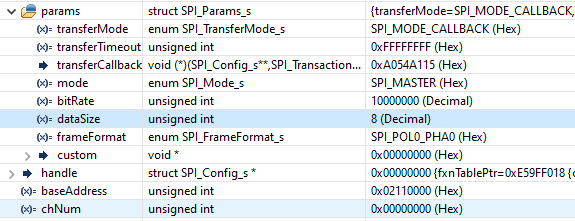

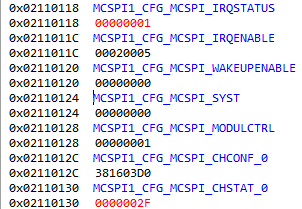

I am testing SPI of AM65X IDK in J20 connector. It is MCSPI1. My code is runing on R5F core and after a little hack of the driver table I can send and receive.

I would like to test DMA and here is my question: is it possible to reach a peripheral in MAIN domain by DMA from MCU domain?

I have found pdk_jacinto_07_00_00\packages\ti\drv\spi\example\mcspi_slavemode\ example and was able to run it with success, but it deals with internally connected spi ports without domain crossing.

Regards,

Kalman