Hi,

I've fabricated a custom board based on AM3352 and 128MB SDRAM (W631GU6MB-12). The PCB is designed according to 7.7.2.3 DDR3 and DDR3L Routing Guidelines from the datasheet.

Unfortunately, I have an issue while booting this custom board:

e2e.ti.com/.../3499621

There are two possible sources of this behavior:

1) U-boot configuration

2) SDRAM timing issue

ad 1)

I did almost everything to investigate this possible cause.

At this moment, I have no idea how I can investigate this further.

I have MLO and U-boot prepared. I use the same MLO and U-boot to boot BeagleBone Black (BBB as a reference test) and my custom board (GW3). BBB boots each time, while the custom board boots 1 per 3 attempts. Detailed description here: e2e.ti.com/.../3499621

ad 2)

I used the EMIF tool to prepare and verify (GEL script) the SDRAM.

I did a memory test using GEL script from EMIF tool. There were no errors detected.

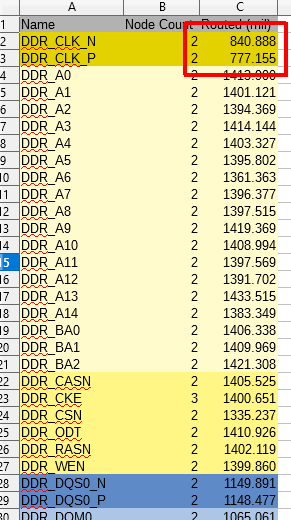

Can I ask for a review of my EMIF spreadsheet:

2086.W631GU6MB_EMIF_Configuration.xlsx

Is it anything suspicious in it?

What can I do to find the source of this issue?

How can I investigate if it is the SDRAM issue?

How can I confirm that it relates to the SDRAM issue?

What are the recommended steps to troubleshoot this issue?

Regards

Adam

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.