Other Parts Discussed in Thread: TMS320DM6437

Hi All,

I would like to ask some questions on EMIF.

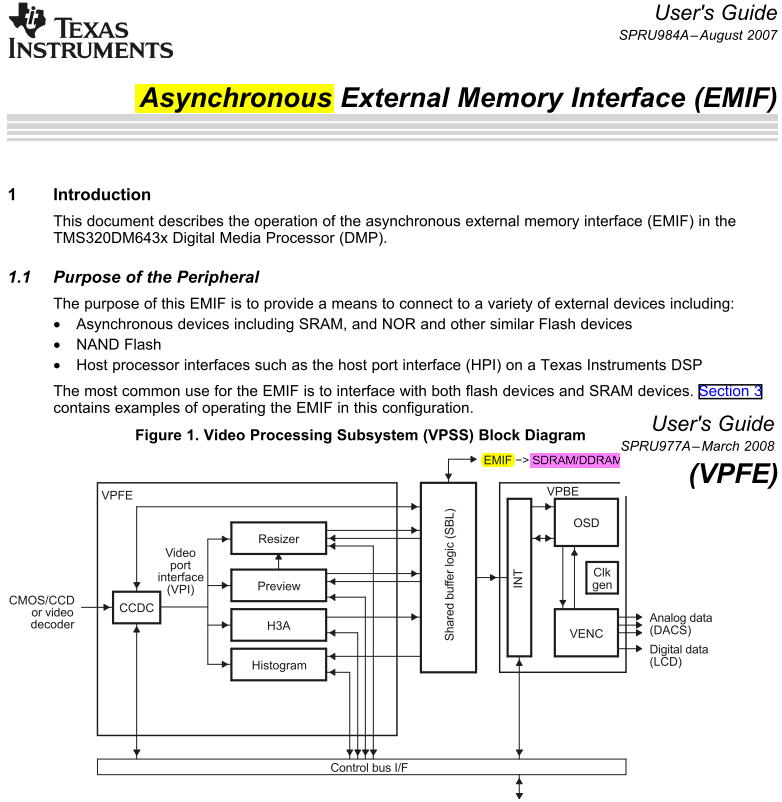

SPRU984a has its full name to be Asynchronous External Memory Interface, but VPFE document says CCDC should be connected via EMIF to SDRAM.

So is SDRAM (of which DDR2 is a special type), whose full name is Synchronous dynamic Random Access Memory, an asynchronous or synchronous device? Isn’t there any inconsistency here?

Thanks,

Zheng