Other Parts Discussed in Thread: TMDSEVM437X, SYSBIOS

Hello,

Regarding to data cache operation by HLOS API with TMDSEVM437X, my customer is asking a question.

When data cache operation(clean) by HLOS API(using inval_Dcache() ), it no response from program at inval_Dcache() call.

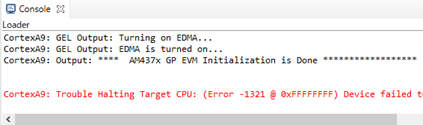

At that time, when “Suspend” buttom (CCS tool bar) is push, the error message is shown following.

「CortexA9: Trouble Halting Target CPU: (Error -1321 @ 0xFFFFFFFF) Device failed to enter debug/halt mode because security settings prevent debug. Power-cycle the board. If error persists, confirm configuration and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 8.2.0.00004)」

(Their conditions are following.)

EVM: TMDSEVM437X (AM437x high security)

CCS:Ver.9.1.0.00010 (Compiler: GNU v7.2.1(Linaro)),

WIN OS : Win10(64bit)

(Their test procedure is following.)

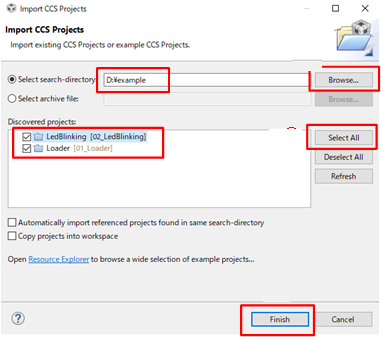

1)They used LedBlinking and Loader project in attached file as test code.

And they put “tiimage.exe” in LedBlinking project folder.

(“tiimage.exe”: https://software-dl.ti.com/processor-sdk-rtos/esd/AM437X/latest/index_FDS.html)

・Loader project: LedBlinking project is translated form OCMC RAM(0x40320000) to DDR SDRAM(0x80000000) and run translated LedBlinking project.

・LedBlinking project: LED3 blinking sample code

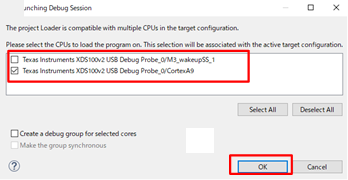

2) Build LedBlinking and Loader project and select target configuration(Loader project). (Below)

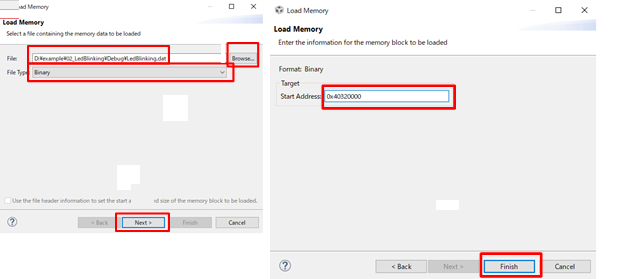

3)After EVM initialization is Done, load ”LedBlinking.dat” (binary) in debug folder by Load Memory in CCS. Start Address is “0x40320000”. (Below)

4)When LedBlinking.dat is download on OCMC RAM, debug start to Loader project.

5) When data cache operation(clean) by HLOS API(using inval_Dcache() ),it no response from program at inval_Dcache() call.

(Before running translated LedBlinking project, data cache operation(clean) has problem.)

6) At that time, when “Suspend” buttom (CCS tool bar) is push, the error message is shown following. (Below)

(Question)

Could you please tell why this problem is occurred and solution for problem?

Could you please give us any comment or advice?

Regards,

Tao_2199