Tool/software: Code Composer Studio

Problem/Error: "

Load Program Error.

...\\simple_audio\Debug\simple_audio.out

Does not match the target endianness, not loaded.

Check project build options and target configuration file (ccxml).

A little background:

I have a DSK6416T board and a customized board of DSK6416T. In my customized board I have used the CPLD, SDRAM, FLASH etc, just as they are in the actual board while removing the UTOPIA, HPI interfaces as we didn't need that. I programmed the CPLD with TI provided VHDL code file just to make my customized board act like a DSK6416T when programming. I have cross checked all interfaces of CPLD and it's working like the DSK CPLD. It generates the CPU clock and EMIF clock perfectly.

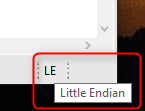

What I am trying to do is to program a simple LED blink code into the customized board which works fine in the DSK6416t board but face the above mentioned error when I try to program the customized DSK6416T board. I am using Texas Instruments XDS100v3 USB Debug Probe JTAG programmer to program both DSK and customized board. The endianness is set to Little on my customized board with the Sw1 set to 0.

I also observed the .GEL file when the CCS try to go into debug mode. It successfully executes the functions in below order:

StartUp()

OnTargetConnect()

OnReset()

OnPreFileLoaded()

and then gives the error on the console : Does not match the target......

When I verify the connections it gives the following details:

[Start]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\IA\AppData\Local\TEXASI~1\CCS\ti\

0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 100- or 510-class product.

This utility will load the adapter 'jioserdesusbv3.dll'.

The library build date was 'Apr 8 2016'.

The library build time was '02:44:08'.

The library package version is '6.0.222.0'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

-----[The log-file for the JTAG TCLK output generated from the PLL]----------

Test Size Coord MHz Flag Result Description

~~~~ ~~~~ ~~~~~~~ ~~~~~~~~ ~~~~ ~~~~~~~~~~~ ~~~~~~~~~~~~~~~~~~~

1 64 - 01 00 500.0kHz O good value measure path length

2 64 + 00 00 1.000MHz [O] good value apply explicit tclk

There is no hardware for measuring the JTAG TCLK frequency.

In the scan-path tests:

The test length was 2048 bits.

The JTAG IR length was 38 bits.

The JTAG DR length was 1 bits.

The IR/DR scan-path tests used 2 frequencies.

The IR/DR scan-path tests used 500.0kHz as the initial frequency.

The IR/DR scan-path tests used 1.000MHz as the highest frequency.

The IR/DR scan-path tests used 1.000MHz as the final frequency.

-----[Measure the source and frequency of the final JTAG TCLKR input]--------

There is no hardware for measuring the JTAG TCLK frequency.

-----[Perform the standard path-length test on the JTAG IR and DR]-----------

This path-length test uses blocks of 64 32-bit words.

The test for the JTAG IR instruction path-length succeeded.

The JTAG IR instruction path-length is 38 bits.

The test for the JTAG DR bypass path-length succeeded.

The JTAG DR bypass path-length is 1 bits.

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End]

One thing that I would like to mention is that my Flash and SDRAM are of from a different company in case if the problem is due to this reason.

DSP Kit SDRAM

| MT48LC2M32B2P-6AAAT:JTR |

| AM29LV400BT-70EC |

Customized board SDRAM

| AS4C2M32SA-6TCN |

| MX29LV400CBTI-70G |

*************************************************************************

Looking for any kind of help from experts. Thanks