Hi,

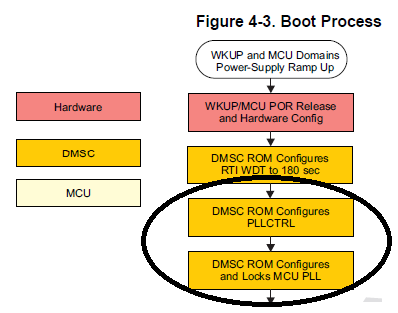

When is exactly the configuration of the MCU PLL executed? According to the Boot Process Flow from chapter 4.2.3 of the Technical Reference Manual, right after the Image Integrity check, the configuration of MAIN Domain PLLs is performed. However, there is no step dedicated to the configuration of MCU Domain PLLs.

Best Regards,

Andrzej