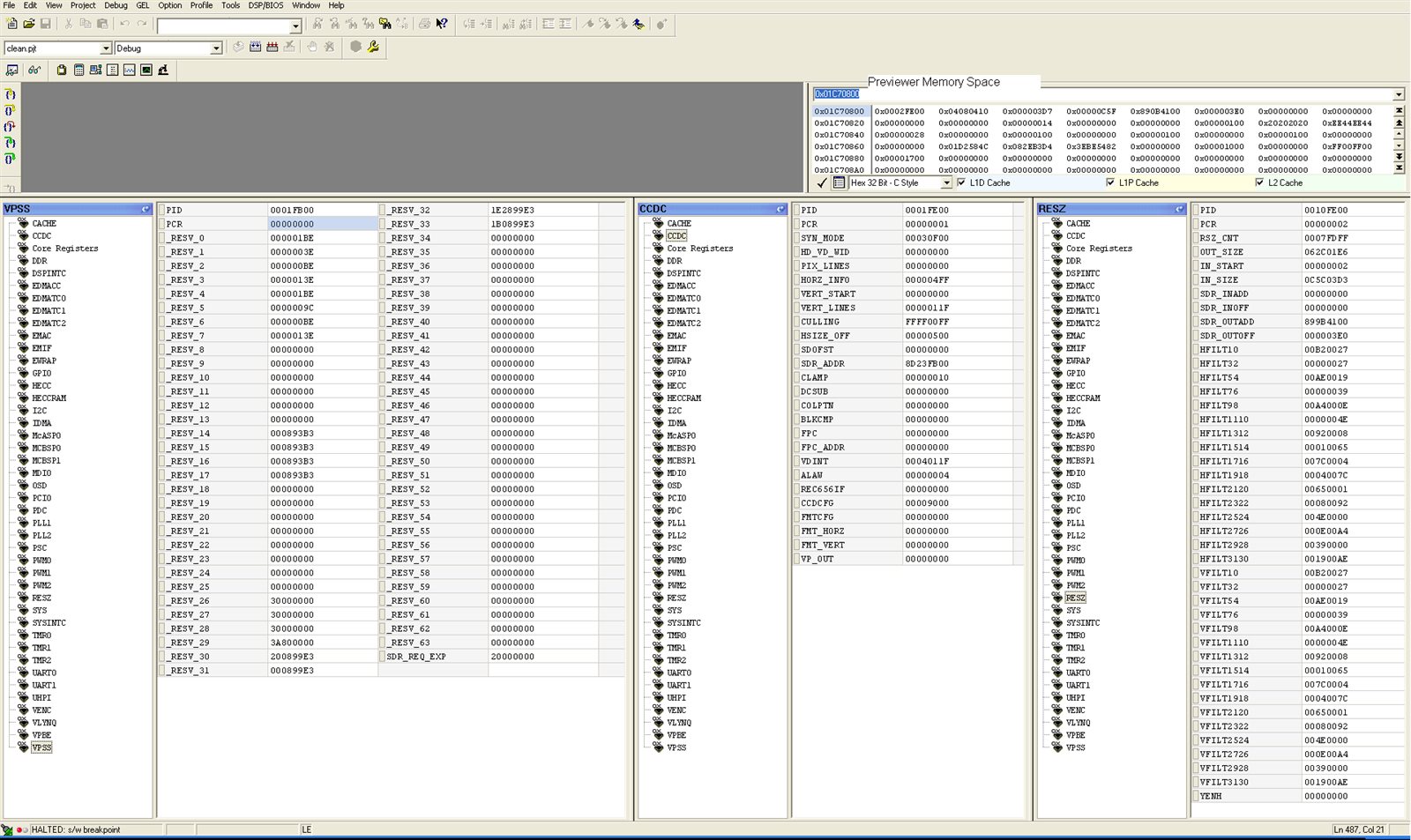

I am still working on trying to push on image through the previewer and resizer in one pass, and I'm getting an output image that looks like a scrambled version of the input, so obviously I haven't set some register up correctly. Question:

Do the horizontal/vertical input size registers of the resizer have to exactly match the horizontal/vertical output sizes of the previewer?