Hello

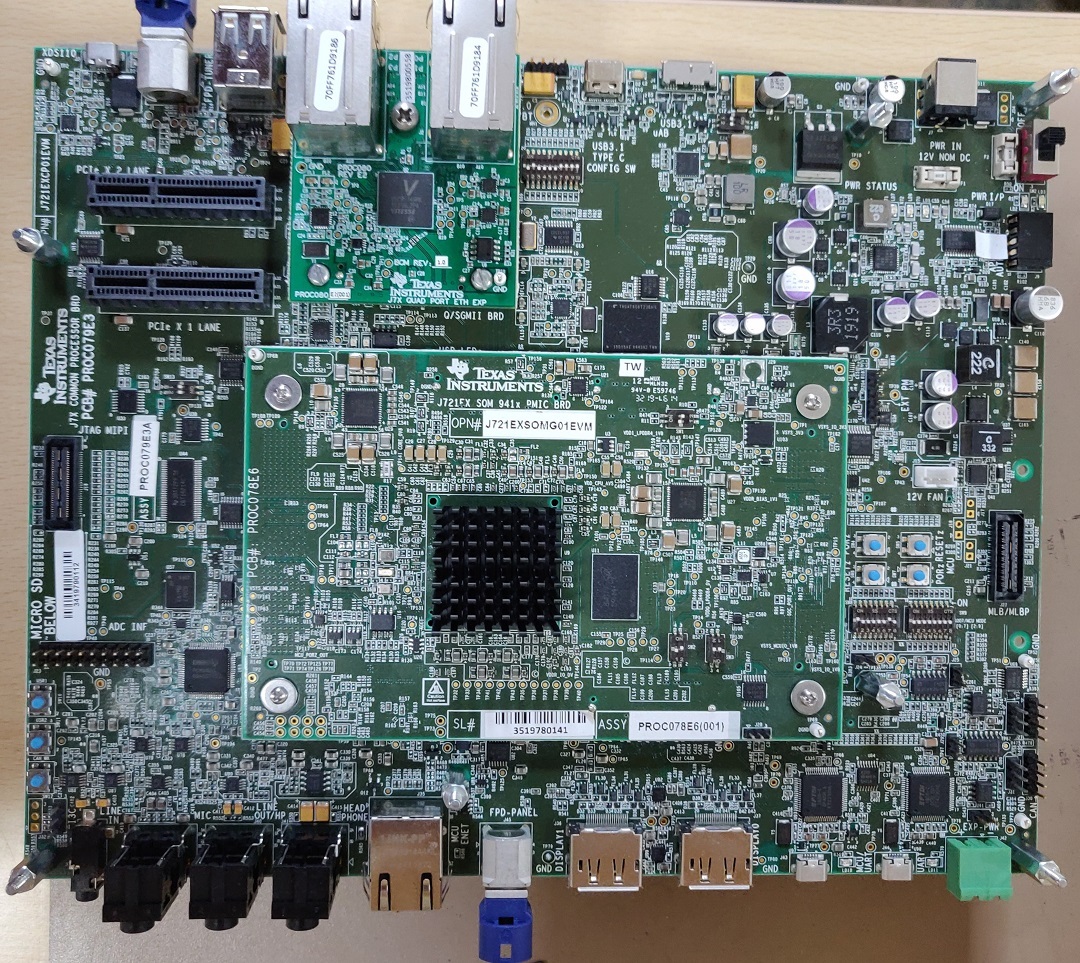

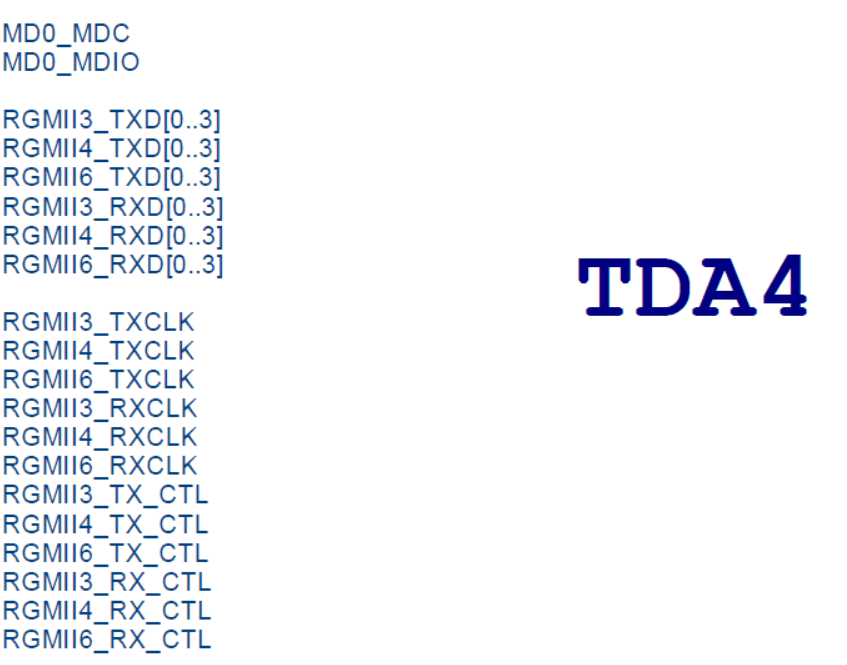

I am upgrading a custom tda4 board with rtl9xxx series PHY on the main r5f, so I plan to use the tda4-evm board to study your code with psdk_rtos_auto_j7_07_00.

After startup, com2 prints as follows:

Enabling clocks for CPSW_9G! CPSW_9G Test on MAIN NAVSS Remote device (core : mcu2_1) ..... Host MAC address: 70:ff:76:1d:87:64 [NIMU_NDK] CPSW has been started successfully Function:app_ethrdev_srv_cb_attach_ext_handler,HostId:0,CpswType:1 Function:app_ethrdev_srv_cb_register_mac_handler,HostId:0,Handle:a2b371c0,CoreKey:38acb7e6, MacAddress:70:ff:76:1d:870 Cpsw_ioctlInternal: CPSW: Registered MAC address.ALE entry:10, Policer Entry:0Function:app_ethrdev_srv_cb_register_ip8 Failed to add Static ARP Entry ================LLI Table entries=========== Number of Static ARP Entries: 0 SNo. IP Address MAC Address ------ ------------- ---------------

Found that IP was not set up successfully, which is inconsistent with the sample tutorial

After consulting the relevant personnel, we know that the vsc8514 board has not been successfully used in your EVM panel, but the daughter card of gei has been successfully used.

Because the EVM board we purchased does not have a Gesi sub card, I can't track the code conversion to my custom board.

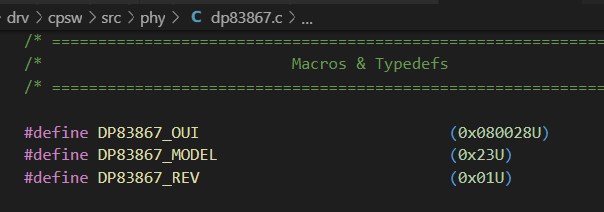

Therefore, I changed the code of dp83867. C and changed its oui, model and Rev.

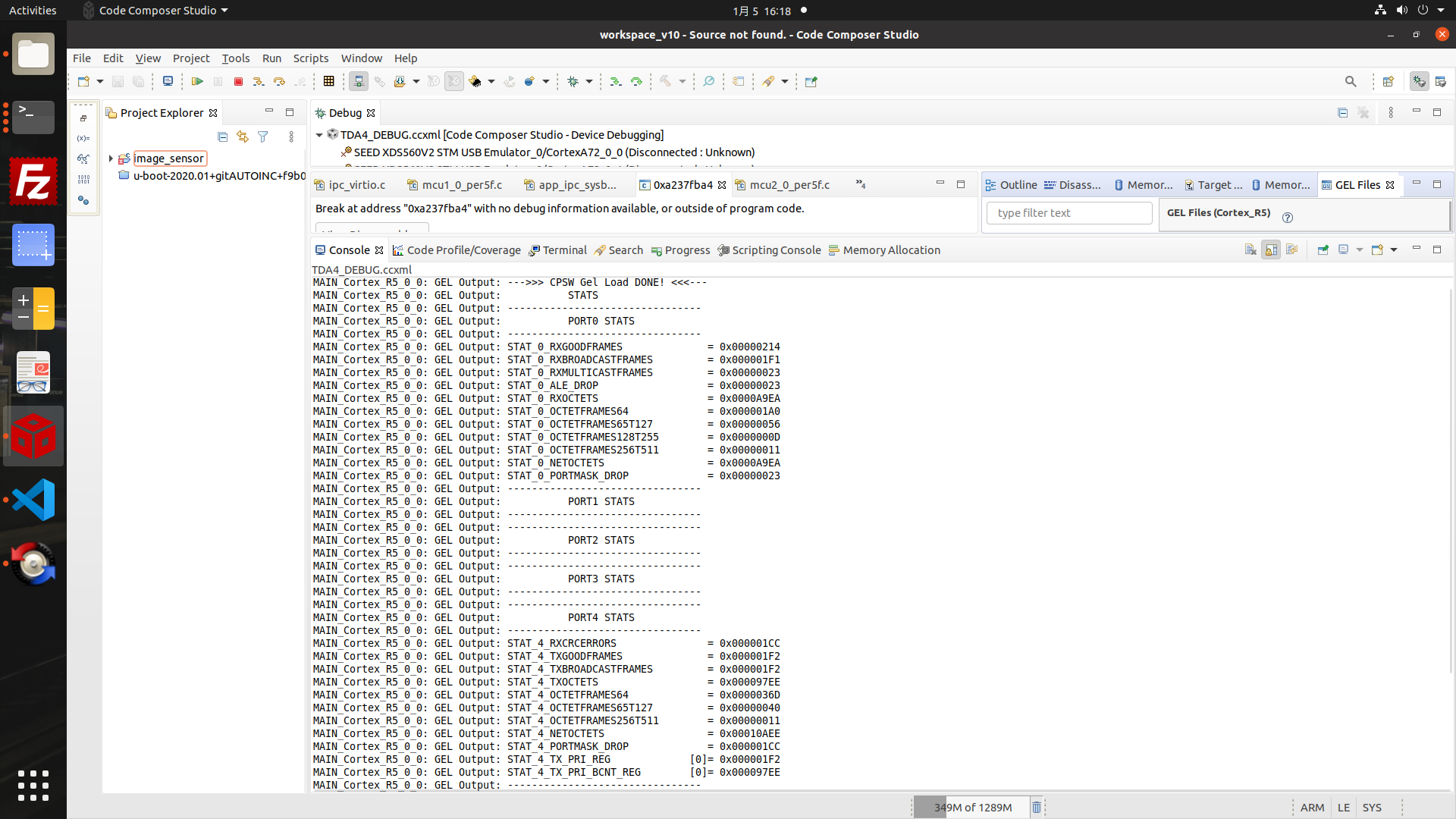

The output of MAIN R5F serial port is as follows:

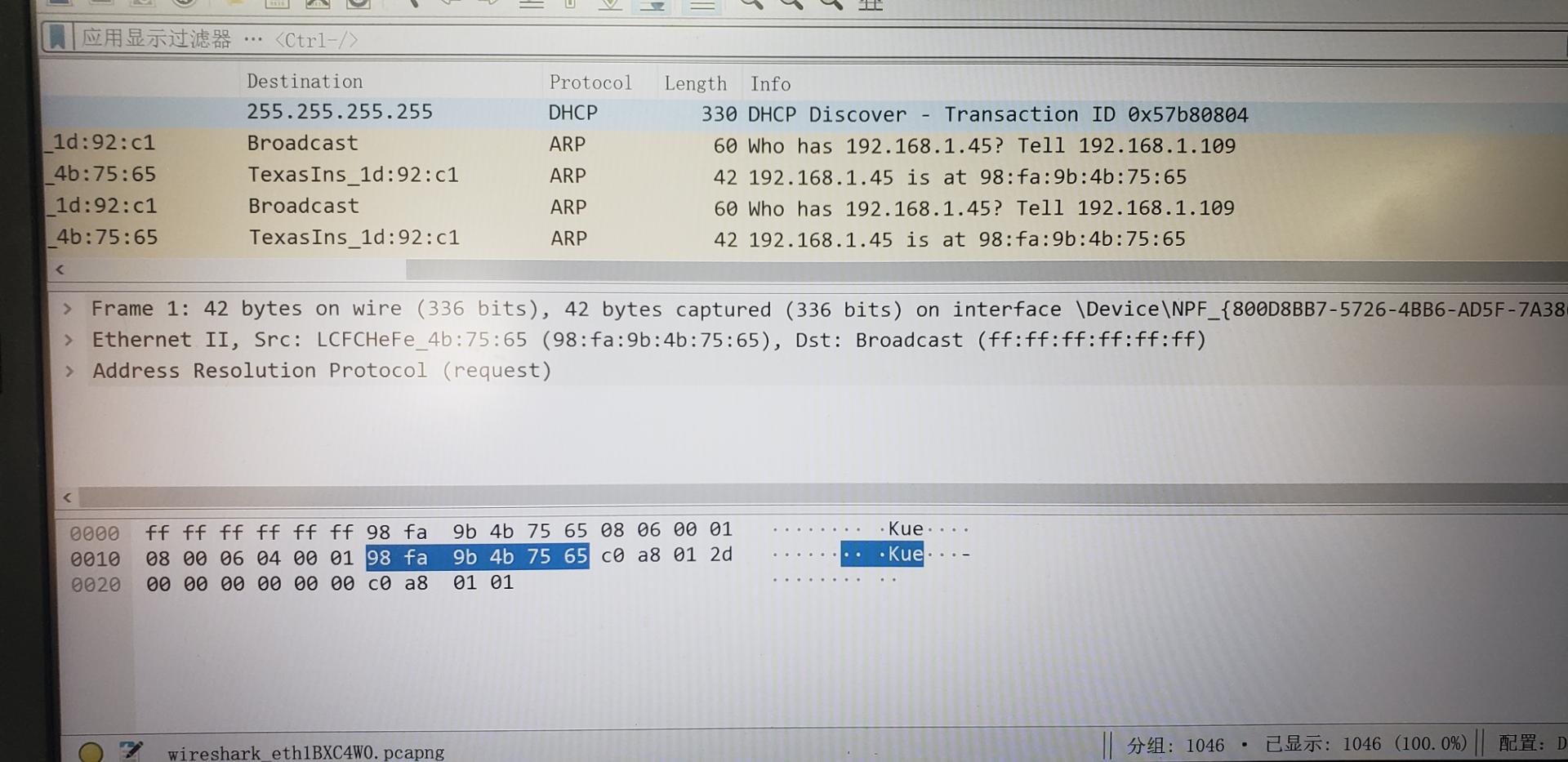

Enabling clocks for CPSW_9G! CPSW_9G Test on MAIN NAVSS Dp83867_isPhyDevSupported: [debug]PHY 0: Dp83867_isPhyDevSupported? it is 1 CpswPhy_bindDriver: PHY 0: OUI:000732 Model:33 Ver:00 <-> 'DP83867' : OK Dp83867_isMacModeSupported: [debug]PHY 0: mode is 3 PHY 0 is alive PHY 1 is alive PHY 2 is alive Remote demo device (core : mcu2_0) ..... Host MAC address: 70:ff:76:1d:92:c2 Function:CpswProxyServer_attachExtHandlerCb,HostId:0,CpswType:1 Host MAC address: 70:ff:76:1d:92:c2 [NIMU_NDK] CPSW has been started successfully Function:CpswProxyServer_registerMacHandlerCb,HostId:0,Handle:a212c53c,CoreKey:3 8acb7e6, MacAddress:70:ff:76:1d:92:c1, FlowIdx:172, FlowIdxOffset:0 Cpsw_ioctlInternal: CPSW: Registered MAC address.ALE entry:11, Policer Entry:0

Found that IP was not set up successfully So I ifconfig its ip

root@j7-evm:~# ifconfig eth1 192.168.1.88

After that,The output of MAIN R5F serial port is as follows:

Function:CpswProxyServer_registerIpv4MacHandlerCb,HostId:0,Handle:a212c53c,CoreKey :38acb7e6, MacAddress:70:ff:76:1d:92:c1 IPv4Addr:192.168.1.88 Failed to add Static ARP Entry ================LLI Table entries=========== Number of Static ARP Entries: 0 SNo. IP Address MAC Address ------ ------------- ---------------

I checked the IP On the A72,:

root@j7-evm:~# ifconfig eth1

eth1 Link encap:Ethernet HWaddr 70:FF:76:1D:92:C1

inet addr:192.168.1.88 Bcast:192.168.1.255 Mask:255.255.255.0

inet6 addr: fe80::72ff:76ff:fe1d:92c1/64 Scope:Link

UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:39 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:6622 (6.4 KiB)

And r5f has been printing as follows:

Function:CpswProxyServer_registerIpv4MacHandlerCb,HostId:0,Handle:a212c53c,CoreKey :38acb7e6, MacAddress:70:ff:76:1d:92:c1 IPv4Addr:192.168.1.88 Failed to add Static ARP Entry ================LLI Table entries=========== Number of Static ARP Entries: 0 SNo. IP Address MAC Address ------ ------------- --------------- DHCP client timed out. Retrying..... DHCP client timed out. Retrying..... DHCP client timed out. Retrying..... DHCP client timed out. Retrying..... DHCP client timed out. Retrying..... DHCP client timed out. Retrying..... DHCP client timed out. Retrying..... DHCP client timed out. Retrying..... DHCP client timed out. Retrying.....

It seems that IP is still not set successfully.

I have a question:

What code do I need to focus on and change to use rtl9010 PHY?

What I know is to get his chip PHY address by checking the chip manual data sheet. Is there anything else?

notes:For some reason, we need to set PHY to 100 Mbps, not adaptive or 1Gbps.