Other Parts Discussed in Thread: AM5728

Hi,

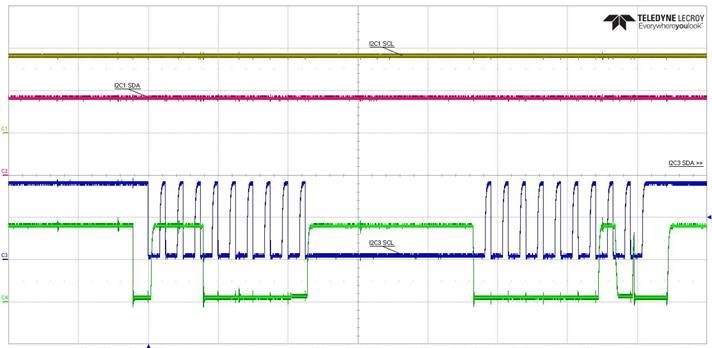

I'm using I2C3 in U-boot.

I2C1 to which PMIC is connected is working fine.

In U-Boot 2018.1 I was able to access devices on I2C3 by enabling the clock in the arch/arm/mach-omap2/omap5hw_data.c, by adding the bold line (as suggested by TI)

...

void enable_basic_clocks(void)

{

...

u32 const clk_modules_explicit_en_essential[] = {

...

(*prcm)->cm_l4per_i2c1_clkctrl,

(*prcm)->cm_l4per_i2c3_clkctrl,

#ifdef CONFIG_DRIVER_TI_CPSW

(*prcm)->cm_gmac_gmac_clkctrl,

I was able to access a chip on I2C3

i2c dev 2

Setting bus to 2

i2c mw 0x70 1.0 1

Now I migrated to U-Boot 2020.1 and I'm getting

i2c mw 0x70 1.0 1

i2c_write: error waiting for data ACK (status=0x116)

Error writing the chip: -121

It seems that the related device tree entry

&i2c3 {

status = "okay";

u-boot,dm-spl;

clock-frequency = <400000>;

is correctly read:

i2c speed

Current bus speed=400000

Any clue what else I need to get I2C3 working?

BR, Chris