Memory-to-memory transfer (block transfer) is performed using UDMA of AM65x.

At that time, when the channel is teardown during data transfer, the channel cannot be used continuously even if the channel is enabled again.

It works fine in the following cases.

1. Channel open (channel configuration)

2. Channel enabled

3. Data transfer (M2M block transfer)

4. Channel disabled (Teardown after all data transfer is completed)

5. Repeat steps 2 to 4

Does not work properly in the following cases

1. Channel open (channel configuration)

2. Channel enabled

3. Data transfer (M2M block transfer)

・ Set multiple transfer data in the free ring queue (example: 64 requests)

・ Start data transfer (64 requests are set to DoorBell)

4. Channel disabled during data transfer

・ Teardown for TX channel

・ After Teardown, re-enable the channel

5. Channel disabled

・ Teardown does not work properly.(Polling the EN bit of UDMA_TRT_CTL_j Register defined in UDMASS_UDMAP0_CFG_TCHANRT, but not disabled)

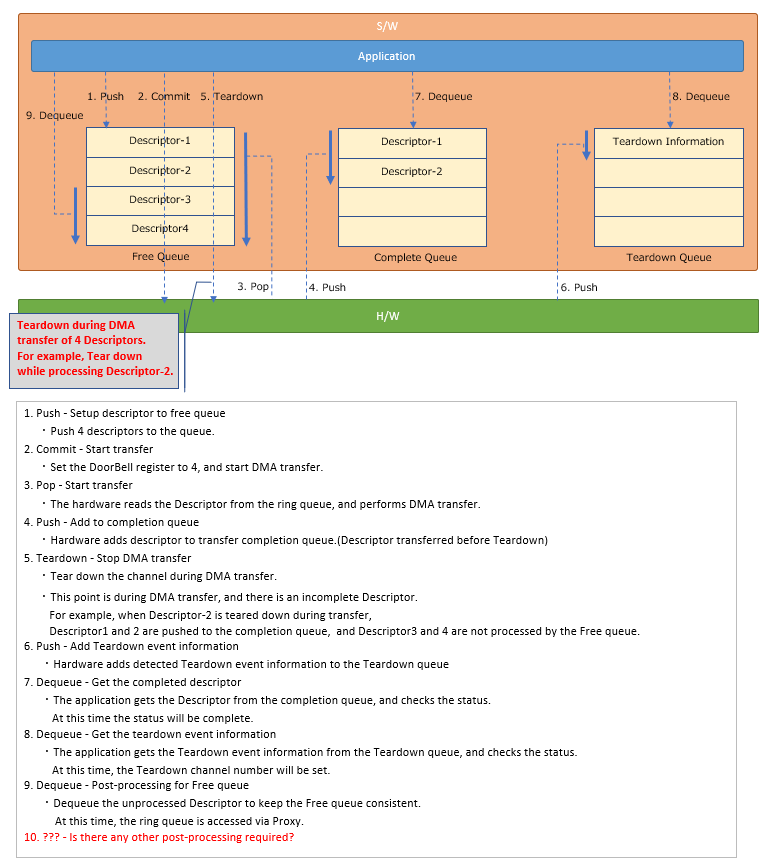

As a post-processing of Teardown during data transfer, the unprocessed request in the free ring queue is popped..

Is there any other post-processing required after Teardown during data transfer?