Hi,

My visionSDK version: 3.08

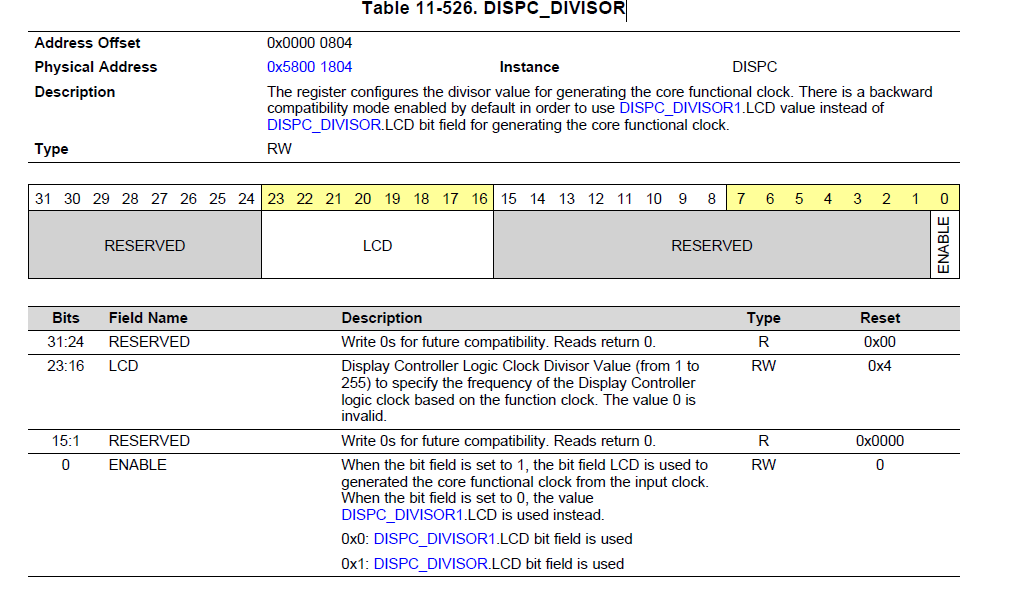

We use DSS to send out YUV422 of vout1 which is based on BT656, and write back pipeline to convert RGB2YUV. It works fine.

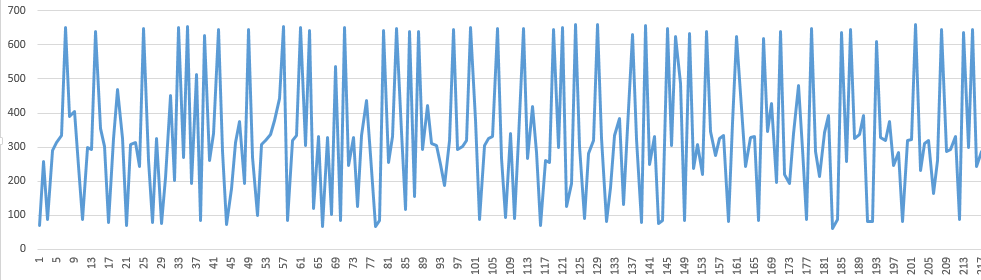

But when I check "Statistics Collector", it shows DSS "Avg Data" is 148.322908 MB/s which is reasonable, and "Peak Data" is 1203.137446 MB/s which is much lager than "Avg Data".

So is it reasonable? Or did I miss something?

Thanks!

BR/TIm