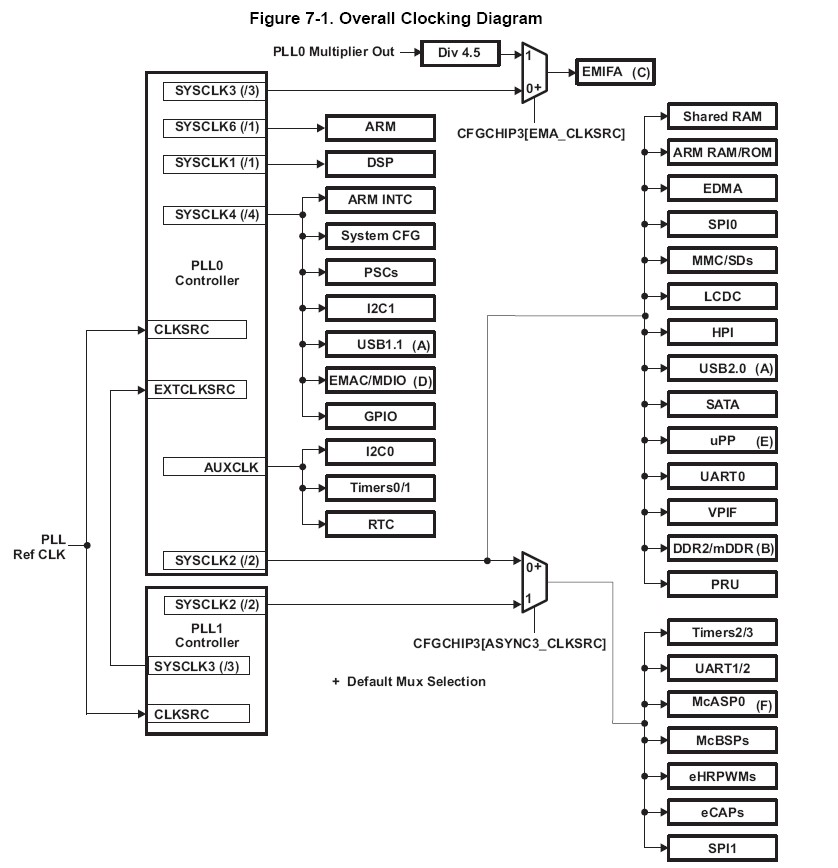

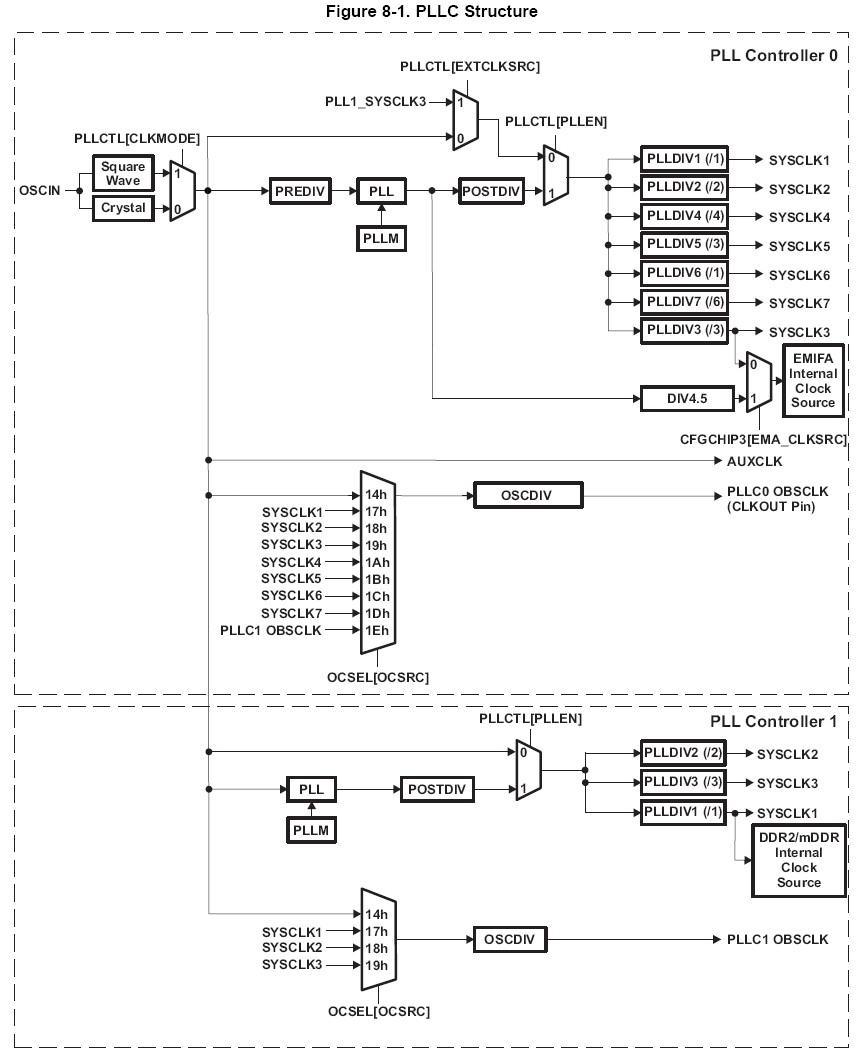

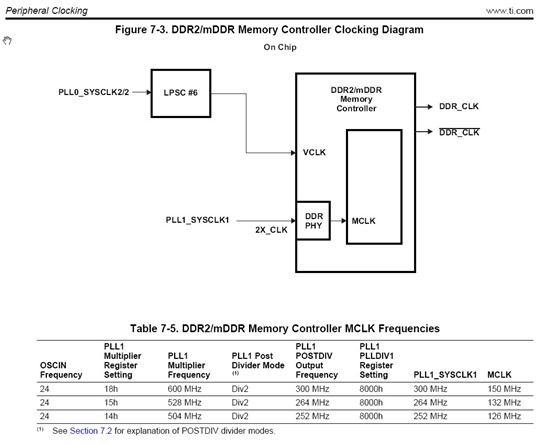

Hello I am currently using both on board PLL controllers to drive all my peripherals. In order to save battery life I am currently investigating the possibility of drive all my peripherals by only using PLL0. However, there seems to be conflicting information within the Freon Reference Guide in regards to the clock tree. Let's take for example the mDDR peripheral. Under Figure 7-1 below, it can only be driven from PLL0, while from under FIgure 8-1, it can only be clocked under PLL1. Is there a single diagram or spreadsheet that I can track for the whole system clock tree with dividers and clock gating registers so that I can ensure that if I do want to change my PLL clocks, I would like to easily indentify which peripherals will be affected.