Other Parts Discussed in Thread: DRA752

Hello champs,

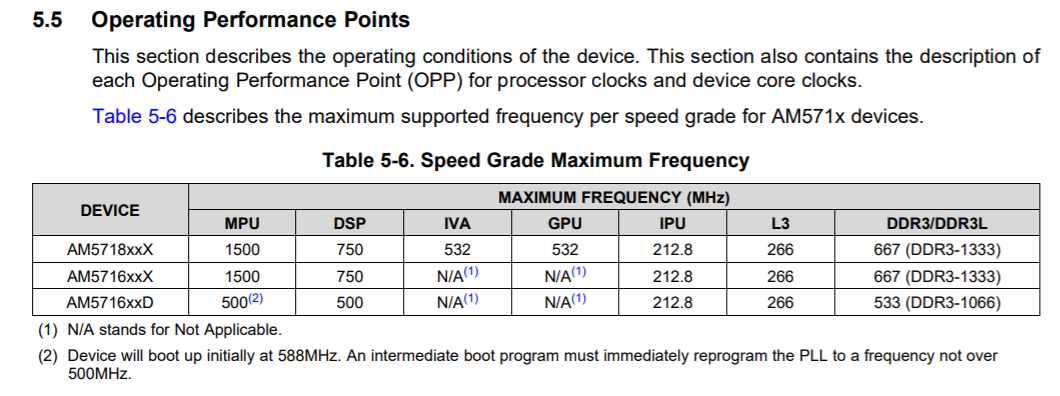

Customer used his own AM5718 board. He failed to upgrade the CPU speed to 1.5GHz.

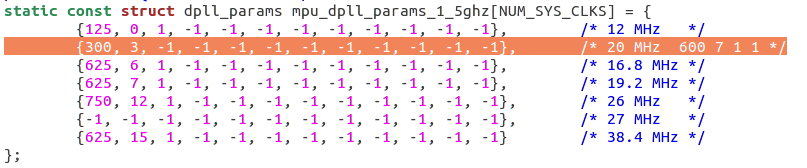

He used debian. He modified mpu_dpll_params_1_5ghz in HW_DATA.C by referencing below website.

https://software-dl.ti.com/processor-sdk-linux/esd/docs/06_03_00_106/linux/How_to_Guides_Linux_Porting_Guide_AM571x_AM570x_Speed_Grades.html

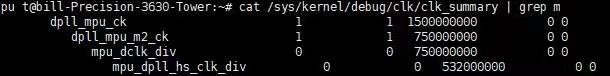

The dpll_mpu_ck is correct but the dpll_mpu_2_ck is only750000000.

He did a few tests as below:

1. Upgrade the clock to 1.2GHz, the system could run for about 12 hours and then down. M=240,N=3,M2=M3=1;

2. Upgrade the clock to 1.3GHz, the system could run for about half an hour and then down. M=260,N=3,M2=M3=1;

3. Upgrade the clock to 1.4GHz, the system could boot up and then down. M=280,N=3,M2=M3=1;

4. Upgrade the clock to 1.5GHz, the system could not boot up, it always reads the MMC1. M=300,N=3,M2=M3=1;;

Dumping the CM_SLKSEL_DPLL_MPU and CM_DIV_M2_DPLL_MPU registers, both of them are correct. DCC_EN=1,DPLL_BYP_CLKSEL=1.

All of his boards and the EVM board from Forlinx have the same issue.

Thanks.

Rgds

Shine