Hello,

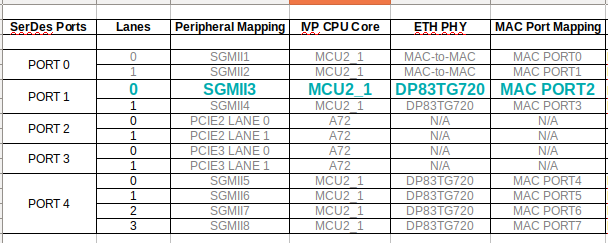

As we talked during our Meeting, I started testing Ethernet Firmware by enabling one PHY at a time. Just for reference, I have disabled all the MAC ports in main_tirtos.c and only enabled "CPSW_MAC_PORT_2" .

With all changes in place ( i.e. clocks for SerDes1, Sgmii MAC-to-PHY bindings, etc.) Once in a while, I see this log -

======================================================

CPSW Ethernet Firmware

======================================================

CPSW_9G Test on MAIN NAVSS

CpswMacPort_configSgmii: MAC 2: Configuring SGMII in SGMII_WITH_PHY mode

CpswPhy_bindDriver: PHY 0: OUI:080028 Model:28 Ver:04 <-> 'dp83tg70' : OK

PHY 0 is alive

PHY 4 is alive

PHY 5 is alive

PHY 8 is alive

PHY 10 is alive

PHY 12 is alive

ETHFW Version : 0.01.01

ETHFW Build Date: Feb 16, 2021

ETHFW Build Time: 16:12:55

ETHFW Commit SHA: 1dc91cd6

Host MAC address: IPC_echo_test (core : mcu2_0) .....

70:ff:76:1d:92:c2

Remote demo device (core : mcu2_0) .....

Host MAC address: EthApp_initIpcTask: Ipc_lateVirtioCreate failed: -1

PHY 0: SGMII_CTRL = 0x027b

70:ff:76:1d:2:c2

PHY 0: RGMII_CTRL = 0x0120

PHY 0: RGMII_DELAY_CTRL = 0x0000

PHY 0: RGMII_DELAY_TX_RX = 0x0980

PHY 0: REG_MasterSlave = 0xc001

CpswPhy_enableState: PHY 0: falling back to manual mode

CpswPhy_enableState: PHY 0: new link caps: FD1000

CPSW has been stated sucesfully

After this, I get this periodic message -

PHY 0: SGMII_CTRL = 0x027b PHY 0: RGMII_CTRL = 0x0120 PHY 0: RGMII_DELAY_CTRL = 0x0000 PHY 0: RGMII_DELAY_TX_RX = 0x0980 PHY 0: REG_MasterSlave = 0xc001 CpswPhy_enableState: PHY 0: falling back to manual mode CpswPhy_enableState: PHY 0: new link caps: FD1000

Based on the log content It looks like the Software is reaching up to Ethernet Caps. However, it is working only once in the 5 power cycles. Most of the time Ethernet firmware sends the following error.

======================================================

CPSW Ethernet Firmware

======================================================

CPSW_9G Test on MAIN NAVSS

Assertion @ Line: 1268 in src/cpsw_macport.c: version.ident_val == ipInfo->sgmiiInfo.versionInfo.moduleId : failed !!!

Could you please let me know what issue I am facing here, and what I have to do to make it stable?

Thanks,

Satish