Part Number: TDA4VM

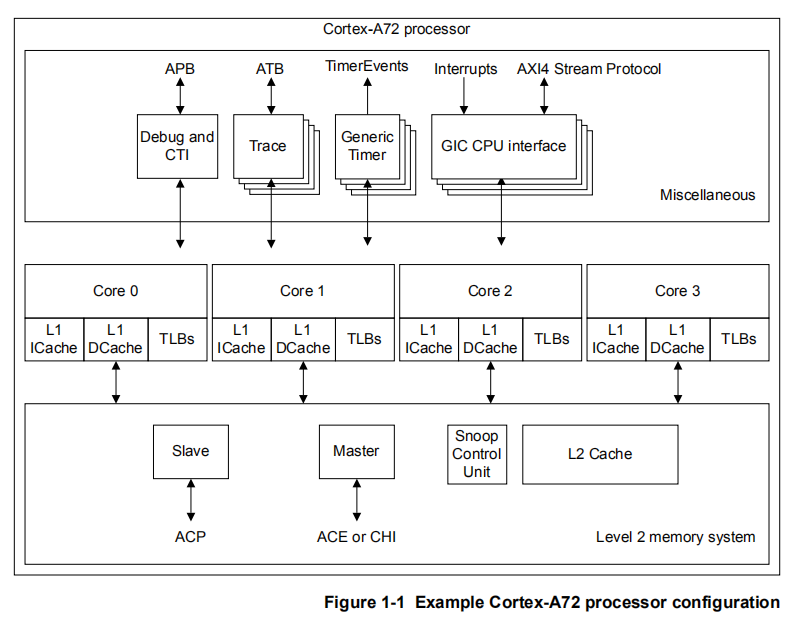

On TDA4VM, there are two instances of the dual-core Arm Cortex-R5F processor and one dual-core Arm Cortex-A72 Microprocessor Unit (MPU) integrated in MAIN domain.

So, there are 2 Arm Cortex-A72 and 4 Arm Cortex-R5F integrated in MAIN domain?

There are 4 cores for each Arm Cortex-A72.

How many Cortex-A72 cores integrated on TDA4vm in total? 2 or 8(2 processors* 4 cores)?

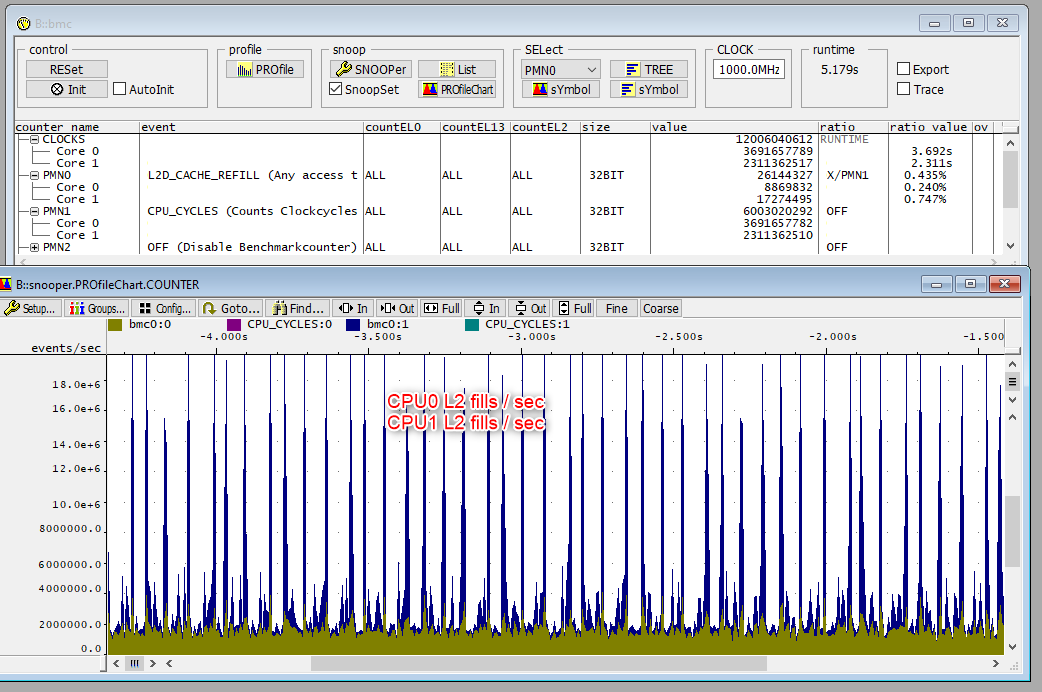

There is one PMU for each core? or there is one PMU for all cores?

If one PMU for all cores, PMU count all cache miss/hit on all cores?