Other Parts Discussed in Thread: SYSBIOS

Hello,

I am trying to generate a PWM signal on the eHRPWM3_A output of the 66AK2G12. I have only just begun writing the code; so far I have only attempted to write to two of the ePWM configuration registers. Here is the function I have written:

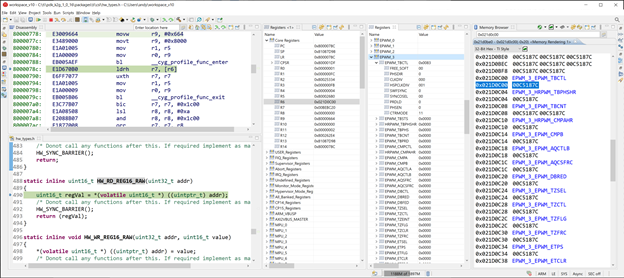

#include "board/board_internal.h"#include <ti/csl/csl_types.h>#include <ti/csl/src/ip/epwm/V0/csl_epwm.h>#include <ti/csl/src/ip/epwm/V0/hw_pwmss_epwm.h>#include <ti/csl/soc/k2g/src/cslr_soc_baseaddress.h>#include <stdint.h>

void lcd_pwm_init(void){ int32_t result; const uint32_t module_clock = 100E6; // 100 Mhz const uint32_t timebase_clock = 12500E3; // 12.5 MHz const uint32_t pwm_freq = 25E3; // 25 kHz

CSL_BootCfgUnlockKicker();

// Configure the clock divider of the Time Base module. CSL_epwmTbTimebaseClkCfg(CSL_PWM_3_CFG_REGS, timebase_clock, module_clock);

// Configure the PWM frequency. CSL_epwmTbPwmFreqCfg(CSL_PWM_3_CFG_REGS, timebase_clock, pwm_freq, CSL_EPWM_TB_COUNTER_DIR_UP, CSL_EPWM_SHADOW_REG_CTRL_DISABLE);

CSL_BootCfgLockKicker();}

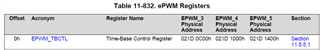

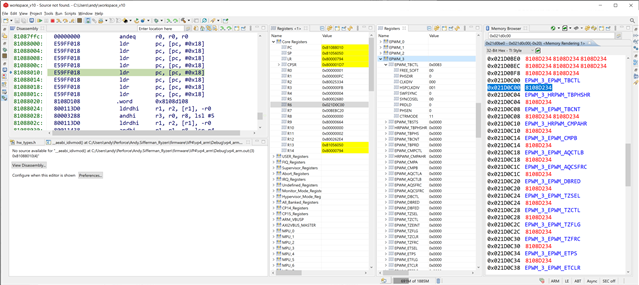

The function CSL_epwmTbTimebaseClkCfg performs a read-modify-write of the EPWM_TBCTL register for ePWM 3. When I single-step through the code, an exception occurs at the moment the hardware register is read.

What am I doing wrong?

Thank you.

Andy