Hello,

I have to implement a custom layer which changes only small part(boundary or center) of input.

I'd like to reuse input buffer to avoid useless IO.

Could guide how to implement such custom layer?

Best regards,

Wilson

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

I have to implement a custom layer which changes only small part(boundary or center) of input.

I'd like to reuse input buffer to avoid useless IO.

Could guide how to implement such custom layer?

Best regards,

Wilson

Hi Wilson,

You can use following parameter which is part of sTIDL_CustomParams_t to indicate whether input and output can overlap for a given layer

/** Parameter specifying whether input and output memory can overlap

* 0: Input cannot be overwritten by output

* 1: Input can be overwritten by input

Note : By default this will be 0

*/

int32_t memOverlapType;

Regards,

Anshu

Anshu,

Thanks for prompt answer. I'll try it and get back if it doesn't work.

Best regards,

Wilson.

Anshu,

I set memOverlapType but address of input/output buffer was not same. Could you check it again?

Best regards,

Wilson.

Hi Wilson,

Can you confirm the version of TIDL or SDK which you are using?

Regards,

Anshu

Hi Wilson,

This parameter should be working with this release. So even after this parameter the input buffer and output buffer are coming different?

Regards,

Anshu

Hi Anshu,

Here is import code. Could you review code?

int32_t TIDL_caffeMapPartialFillerParams(sTIDL_OrgNetwork_t *pOrgTIDLNetStructure,

int32_t i,

int32_t& layerIndex,

int32_t& dataIndex,

NetParameter& netStructure,

NetParameter& netParams) {

sTIDL_LayerPC_t &TIDLPCLayers = pOrgTIDLNetStructure->TIDLPCLayers[layerIndex];

sTIDL_CustomParams_t &customParams = pOrgTIDLNetStructure->TIDLPCLayers[layerIndex].layerParams.customParams;

TIDLPCLayers.layerType = TIDL_CustomLayer;

TIDLPCLayers.numInBufs = 1;

TIDLPCLayers.numOutBufs = 1;

TIDLPCLayers.outData[0].dataId = dataIndex++;

customParams.customLayerType = TIDL_CUSTOM_TYPE_SV_PARTIAL_FILLER;

customParams.memOverlapType = 1; //must be overlapped

//customParams.doesLayerChangePadding = 0;

//get parameter.

TIDL_CustomParamsPartialFiller_t *od_partial_filler_params = (TIDL_CustomParamsPartialFiller_t *)malloc(sizeof(TIDL_CustomParamsPartialFiller_t));

TIDLPCLayers.weights.ptr = (void*)od_partial_filler_params;

TIDLPCLayers.weights.bufSize = sizeof(TIDL_CustomParamsPartialFiller_t);

od_partial_filler_params->x1 = netStructure.layer(i).partial_filler_param().fill_range_param(0).xbegin();

od_partial_filler_params->y1 = netStructure.layer(i).partial_filler_param().fill_range_param(0).ybegin();

od_partial_filler_params->x2 = netStructure.layer(i).partial_filler_param().fill_range_param(0).xend();

od_partial_filler_params->x2 = netStructure.layer(i).partial_filler_param().fill_range_param(0).yend();

return 0;

}

When I run with generated bin file, input was [0x7fff39882010] ~ [0x7fff399d2d4e] and output was [0x7fff4106f0ba] ~ [0x7fff411bea3a].

Best regards,

Wilson.

Hi Wilson,

Do input and output dimension changes with the processing which you are doing? Or they are expected to remain the same.

Regards,

Anshu

Hi Anshu,

Input and output must be same. Custom layer fills very small part of input by zero.(padding clear)

Best regards,

Wilson

Hi Wilson,

Does it mean that the output buffer has extra padding compared to input buffer?

Can you try the following parameter

doesLayerChangePadding = 0

Set padW and padH values as per the padding required by the custom layer.

Regards,

Anshu

Hi Anshu,

I already tried "doesLayerChangePadding=0". It didn't work.

What I want is that one buffer is used for input/output of custom layer. In Vision SDK, it was called "in-place queue mode".

Best regards,

Wilson.

Hi Wilson,

In you code I don't see that you are setting padW and padH values. Given that you expect padding to be available in the buffer this should be set. The way input and output overlap works is first it checks whether a particular layer can overwrite the input which for custom layer is communicated via memOverlapType. Once input and output can overlap then the logic checks if the buffer arrangements and the dataflow allows overlap or not. I think in your case this second condition is not meeting and I am suspecting its because of the padding. Can you tell us input and output buffer layout in your case?

If you can share bufInfolog.txt ( this should be generated at the same location where network compiler information is generated), it might help to figure out why overlap is not happening.

Regards,

Anshu

Hi Anshu,

Here is bufinfolog.txt. Layer 1 and 3 are custom layers needs in-place update. Output of custom layer is input of conv5x5 or conv3x3, so they need padding. In run-time, custom layer's in/out buffer has same padding but pitch values are different.

------Layer #(Type) [Exec ID , Data ID] --[Ni x inW x inH] => [No x outW x outH] [Ni/G] [dataflowType] [preFetch, preFetchAlign, procSize, inPlaneSize] [dmaFreq] [dmaFreqWt] [kernelFreq] [In Data Ids] ----- ------ 0( Data) [0, 0] --[0 x 0 x 0] => [3 x 1760 x 256] *** [0] ***[FRAME] ***[0, 0, 1, 0]**** [0], [1],[1] -[]--- DDR, DMA, 6fd8a(458122), 0( 0), 24( 36), 14fd00(1375488), 0, 3a |||| L2, DMA, 0( 0), 0( 0), 0( 0), 0( 0), 0, 0 NONE, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff |||| DDR, DMA, 6fd8a(458122), 6fd8a(458122), 3( 3), 14fd00(1375488), dc6, 3a NONE, NA, 0( 0), 0( 0), 24( 36), 0( 0), 0, 1bc00 |||| L2, CPU, 0( 0), 0( 0), 0( 0), 0( 0), 0, 0 L2, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff Padding Info [Row, Col]: Actual IN -> OUT : [ 0, 0] -> [ 2, 2], Required OUT : [ 2, 2], To fill zero OUT: [ 0, 0] ------ 1( Custom) [1, 1] --[3 x 1760 x 256] => [3 x 1760 x 256] *** [3] ***[ COL] ***[0, 0, 225536, 451072]**** [6], [6],[6] -[0 ]--- DDR, DMA, 6fd8a(458122), 6fd8a(458122), 3( 3), 14fd00(1375488), dc6, 3a |||| L2, DMA, 6e200(451072), 6e200(451072), 1( 1), 6e200( 451072), 0, 0 NONE, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff ||||MSMC, CPU, 6fd8a(458122), 6fd8a(458122), 3( 3), 14f980(1374592), dc6, 3a DDR, DMA, 0( 0), 0( 0), 24( 36), 0( 0), 0, 1bc00 |||| L2, DMA, 0( 0), 0( 0), 0( 0), 0( 0), 0, 6e200 L2, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff Padding Info [Row, Col]: Actual IN -> OUT : [ 2, 2] -> [ 2, 2], Required OUT : [ 2, 2], To fill zero OUT: [ 2, 2] ------ 2( Conv) [2, 2] --[3 x 1760 x 256] => [7 x 880 x 128] *** [3] ***[ROW_C] ***[5288, 5288, 59908, 458122]**** [8], [1],[8] -[1 ]--- MSMC, DMA, 6fd8a(458122), 6fd8a(458122), 3( 3), 14f980(1374592), 0, 3a |||| L2, DMA, 20000(131072), 20000(131072), 3( 3), 60000( 393216), 0, 0 NONE, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff ||||MSMC, CPU, 1c740(116544), 1c6ca(116426), 7( 7), c7380( 816000), 6e6, 14f99a DDR, DMA, 4c( 76), 4c( 76), 7( 7), 280( 640), 0, 1bc00 |||| L2, DMA, c0( 192), 4c( 76), 7( 7), 580( 1408), 0, 60000 L2, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff Padding Info [Row, Col]: Actual IN -> OUT : [ 2, 2] -> [ 2, 2], Required OUT : [ 0, 0], To fill zero OUT: [ 0, 0] ------ 3( Custom) [3, 3] --[7 x 880 x 128] => [7 x 880 x 128] *** [7] ***[ COL] ***[0, 0, 112894, 112896]**** [7], [1],[7] -[2 ]--- MSMC, DMA, 1c740(116544), 1c6ca(116426), 7( 7), c7380( 816000), 6e6, 14f99a |||| L2, DMA, 1c740(116544), 1c740(116544), 2( 2), 38e80( 233088), 0, 0 NONE, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff ||||MSMC, CPU, 1c740(116544), 1c6ca(116426), 7( 7), c7380( 816000), 6e6, 1a DDR, DMA, 0( 0), 0( 0), 54( 84), 0( 0), 0, 1be80 |||| L2, DMA, 0( 0), 0( 0), 0( 0), 0( 0), 0, 38e80 L2, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff Padding Info [Row, Col]: Actual IN -> OUT : [ 2, 2] -> [ 2, 2], Required OUT : [ 1, 1], To fill zero OUT: [ 1, 1]Best regards,

Wilson.

Wilson,

Can you share a representative model that I can use to reproduce the issue locally? When you do this, please share the import config etc and also the patch to configure custom layer.

I tried to understand the issue by looking at the bufinfolog, but it is not very clear to me exactly which layers are supposed to overlap.

- Subhajit

Wilson, I have downloaded your zip file. It looks like you have some changes on top of tidlModelImport, and you have sv_caffeImport. Can you please provide me a patch file instead of the entire folder? That would help me try this out on top of the latest code base.

To create a patch, do the following:

download and install SDK in a new directory

cd tidl_01_03_00_11

git init

git add .

git commit -sm "initial commit"

copy contents from your modified tidlModelImport directory into this folder. Then

git commit -asm "stradvision changes"

git format-patch -1

Once the patch is generated, share with us so that we can make appropriate stradvision related changes on tp of the most recent codebase.

- Subhajit

Wilson,

Thanks for sharing the patch. I have applied your patch on top of our 7.1 codebase.

While compiling I see a build error for tidl_caffeImport_v2.cpp. How to work arrounf this?

$ TIDL_GRAPHVIZ_PATH=/usr PSDK_INSTALL_PATH=$(pwd)/.. make protos it nc gv STRADVISION=1 TARGET_PLATFORM=PC TARGET_BUILD=debug SHOW_COMMANDS=1

.

======== MAKING IMPORT TOOL PROTOS LIB =================

make -C ./ti_dl/utils/tidlModelImport -f makefile_lib

make[1]: Entering directory '/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/utils/tidlModelImport'

mkdir -p ".\lib" || cd ".\lib"

gcc-ar-5 rvs ./lib/libsv_tidl_model_protos.a /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/device_attributes.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/types.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/node_def.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/op_def.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/cost_graph.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/allocation_description.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/attr_value.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/kernel_def.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/graph.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/function.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/log_memory.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/tensor_shape.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/versions.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/tensor_slice.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/tensor_description.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/variable.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/step_stats.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/summary.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/resource_handle.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/tensor.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../onnxImport/onnx_cc/onnx/onnx-operators-ml.proto3.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../onnxImport/onnx_cc/onnx/onnx-ml.proto3.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/faster_rcnn.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/square_box_coder.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/matcher.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/graph_rewriter.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/faster_rcnn_box_coder.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/ssd_anchor_generator.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/anchor_generator.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/argmax_matcher.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/box_coder.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/grid_anchor_generator.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/preprocessor.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/image_resizer.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/model.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/input_reader.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/optimizer.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/box_predictor.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/bipartite_matcher.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/post_processing.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/multiscale_anchor_generator.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/mean_stddev_box_coder.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/losses.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/ssd.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/region_similarity_calculator.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/pipeline.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/string_int_label_map.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/train.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/keypoint_box_coder.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/hyperparams.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/eval.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../sv_caffeImport/caffe.pb.obj /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tidlMetaArch/tidl_meta_arch.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/device_attributes.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/types.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/node_def.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/op_def.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/cost_graph.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/allocation_description.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/attr_value.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/kernel_def.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/graph.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/function.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/log_memory.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/tensor_shape.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/versions.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/tensor_slice.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/tensor_description.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/variable.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/step_stats.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/summary.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/resource_handle.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/proto_cc/tensorflow/core/framework/tensor.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../onnxImport/onnx_cc/onnx/onnx-operators-ml.proto3.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../onnxImport/onnx_cc/onnx/onnx-ml.proto3.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/faster_rcnn.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/square_box_coder.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/matcher.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/graph_rewriter.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/faster_rcnn_box_coder.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/ssd_anchor_generator.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/anchor_generator.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/argmax_matcher.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/box_coder.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/grid_anchor_generator.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/preprocessor.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/image_resizer.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/model.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/input_reader.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/optimizer.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/box_predictor.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/bipartite_matcher.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/post_processing.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/multiscale_anchor_generator.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/mean_stddev_box_coder.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/losses.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/ssd.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/region_similarity_calculator.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/pipeline.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/string_int_label_map.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/train.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/keypoint_box_coder.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/hyperparams.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tfImport/models_research_cc/object_detection/protos/eval.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../sv_caffeImport/caffe.pb.obj

r - /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/../tidlMetaArch/tidl_meta_arch.pb.obj

make[1]: Leaving directory '/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/utils/tidlModelImport'

.

======== MAKING IMPORT LIBS =================

make -C ./ti_dl/utils/tidlModelImport -f makefile_shared

make[1]: Entering directory '/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/utils/tidlModelImport'

STRADVISION 1

OZ_TIDL_PATH

echo compiling tidl_caffeImport_v2.cpp

compiling tidl_caffeImport_v2.cpp

g++-5 -c -D__C7100__ -std=c++14 -ggdb -ggdb3 -gdwarf-2 -DHOST_EMULATION -w -D_HOST_BUILD -DGCC_BUILD -fPIC -DCORE_DSP -D_TMS320C6600 -DLITTLE_ENDIAN_HOST -I "/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/../protobuf-3.5.1"/src -I "/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/../flatbuffers-1.12.0"/include -I ../../inc -I ../sv_caffeImport -I ../tidlMetaArch -I ../tfImport -I ../tfImport/proto_cc -I ../onnxImport/onnx_cc -I ../tfImport/models_research_cc -I ../../../common -I ../../custom -I ../perfsim -I ../tfliteImport -I . -I /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/.. -D_GNU_SOURCE -DTIDL_IMPORT_TOOL -w -I /include -I /src -I /include -I /src tidl_caffeImport_v2.cpp -o /home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/tidl_caffeImport_v2.obj

tidl_caffeImport_v2.cpp: In function ‘int TIDL_caffeConvertCaffemodelToFloat(caffe::NetParameter&)’:

tidl_caffeImport_v2.cpp:573:39: error: ‘const class caffe::BlobProto’ has no member named ‘has_raw_data’

if (netParams.layer(i).blobs(j).has_raw_data())

^

tidl_caffeImport_v2.cpp:575:9: error: ‘Type’ was not declared in this scope

Type raw_type = netParams.layer(i).blobs(j).raw_data_type();

^

tidl_caffeImport_v2.cpp:576:63: error: ‘const class caffe::BlobProto’ has no member named ‘raw_data’

const ::std::string& hd = netParams.layer(i).blobs(j).raw_data();

^

tidl_caffeImport_v2.cpp:577:13: error: ‘raw_type’ was not declared in this scope

if (raw_type == caffe::FLOAT)

^

tidl_caffeImport_v2.cpp:577:25: error: ‘FLOAT’ is not a member of ‘caffe’

if (raw_type == caffe::FLOAT)

^

tidl_caffeImport_v2.cpp:577:25: note: suggested alternative:

In file included from ./tidl_import_config.h:67:0,

from tidl_import_api.h:63,

from tidl_caffeImport_v2.cpp:76:

../../../common/configparser.h:77:3: note: ‘FLOAT’

FLOAT = 4

^

/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/makerules/rules.mk:509: recipe for target '/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/tidl_caffeImport_v2.obj' failed

make[1]: *** [/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/out/PC/dsp/algo/debug/ti_dl/utils/tidlModelImport/tidl_caffeImport_v2.obj] Error 1

make[1]: Leaving directory '/home/subhajit/Works/tidl/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/utils/tidlModelImport'

makefile:255: recipe for target 'it_lib' failed

make: *** [it_lib] Error 2

Hi,

I have applied your new patch, and it applies cleanly.

Then I use the following build command, and I see no errors, so the build went fine,

TIDL_GRAPHVIZ_PATH=/usr PSDK_INSTALL_PATH=$(pwd)/.. make protos it nc gv STRADVISION=1 TARGET_PLATFORM=PC TARGET_BUILD=debug SHOW_COMMANDS=1

After this I tried the import command as specified, but it could not find the executable

$ ./out/sv_tidl_model_import.out ../../test/testvecs/svnet/tidl_import_svnet_od_t215_tiling_448+32+1280x256.txt

bash: ./out/sv_tidl_model_import.out: No such file or directory

So, I tried importing using the TIDL import tool, and I get this error

$ ./out/tidl_model_import.out ../../test/testvecs/svnet/tidl_import_svnet_od_t215_tiling_448+32+1280x256.txt

Caffe Network File : ../../test/testvecs/svnet/caffe/T215_deploy_tiling_448+32+1280x256.prototxt

Caffe Model File : ../../test/testvecs/svnet/caffe/T215.caffemodel

TIDL Network File : ../../test/testvecs/svnet/bin/tidl_svnet_od_t215_tiling_448+32+1280x256_net.bin

TIDL IO Info File : ../../test/testvecs/svnet/bin/tidl_svnet_od_t215_tiling_448+32+1280x256_io_

[libprotobuf ERROR google/protobuf/text_format.cc:288] Error parsing text-format caffe.NetParameter: 15:26: Message type "caffe.LayerParameter" has no field named "partial_filler_param".

ERROR: google::protobuf::TextFormat::Parse proto file(../../test/testvecs/svnet/caffe/T215_deploy_tiling_448+32+1280x256.prototxt) FAILED !!!

Can you suggest me a reason / fix for this issue?

Regards,

Subhajit

Hi Subhajit

Please check the below steps for using sv_import tool

1. check that two patches that shared by us are applied

dongwon@builder:/home/user/Desktop/Datastorage2/dongwon/ws_psdk_7_1/tidl_req/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11$ git log

commit 8bc8145bb31a96525b19b6ccded467d8d14371ad (HEAD -> master)

Author: Dongwon Choi <dongwon.choi@stradvision.com>

Date: Tue Jun 8 14:36:38 2021 +0900

stradvision changes (build sv_tidl_model_import.out)

commit 3c0fb82f82c3c9019a110ecc0024a0a4b107dc43

Author: Dongwon Choi <dongwon.choi@stradvision.com>

Date: Thu Jun 3 13:29:06 2021 +0900

stradvision changes

Signed-off-by: Dongwon Choi <dongwon.choi@stradvision.com>

commit 87d20415dc46fc6e4fbcd92e018e14ca0640b22e

Author: Dongwon Choi <dongwon.choi@stradvision.com>

Date: Thu Jun 3 13:22:50 2021 +0900

initial commit

Signed-off-by: Dongwon Choi <dongwon.choi@stradvision.com>

2. remove all object files for clean build

dongwon@builder:/home/user/Desktop/Datastorage2/dongwon/ws_psdk_7_1/tidl_req/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11$ rm -rf out/ dongwon@builder:/home/user/Desktop/Datastorage2/dongwon/ws_psdk_7_1/tidl_req/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11$ rm -rf ti_dl/utils/tidlModelImport/lib/ dongwon@builder:/home/user/Desktop/Datastorage2/dongwon/ws_psdk_7_1/tidl_req/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11$ rm -rf ti_dl/utils/tidlModelImport/out/

3. build

dongwon@builder:/home/user/Desktop/Datastorage2/dongwon/ws_psdk_7_1/tidl_req/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11$ TIDL_GRAPHVIZ_PATH=/usr PSDK_INSTALL_PATH=$(pwd)/.. make protos it nc gv STRADVISION=1 TARGET_PLATFORM=PC TARGET_BUILD=debug SHOW_COMMANDS=1

4. make directory for bin files and run sv import tool

ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11$ mkdir -p ti_dl/test/testvecs/svnet/bin/

ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11$ cd ti_dl/utils/tidlModelImport/

tidl_req/ti-processor-sdk-rtos-j721e-evm-07_01_00_11/tidl_j7_01_03_00_11/ti_dl/utils/tidlModelImport$ ./out/sv_tidl_model_import.out ../../test/testvecs/svnet/tidl_import_svnet_od_t215_tiling_448+32+1280x256.txt

You can find the imported model files at tidl_j7_01_03_00_11/ti_dl/test/testvecs/svnet/bin directory

tidl_svnet_od_t215_tiling_448+32+1280x256_net.bin

tidl_svnet_od_t215_tiling_448+32+1280x256_io_1.bin

Regards

Dongwon Choi

Dongwon,

I could successfully reproduce the issue. Thanks!

Let me clarify that layer 1 cannot overlap with layer 0 as layer 0 is input to the model and the buffer is in DDR, whereas layer 1 is an intermediate custom layer with the output buffer in MSMC.

I hope that clears the question of why layer 1 is not overlapping with layer 0

I am currently investigating why layer 3 does not overlap with layer 2 and I will update on this.

- Subhajit

Hi Dongwon,

Though output of layer 3 does not overlap with its input, it shouldn't impact performance. Because both buffers are still in MSMC (on chip memory). The reason for them not being overlapped is tied to internal allocation logic which is more opportunistic on need basis.

From end user point of view I don't see any impact of layer 3 not being overlapped.

For layer 1, reason for not overlapping is already explained by Subhajit. Basically we first try to be on faster memory ( on chip ) if available. If not then only go to DDR. If layer 1 output couldn't fit in on-chip memory then only we would have tried to go to DDR and respected the overlap behavior

Also your statement in first post (reproduced below) is not valid even if the input/output buffer overlaps. Still the IO (read and write access happen), but the memory size requirement reduces. SO just want to clarify that overlap doesn't help in memory bandwidth reduction and only helps in memory size requirement

"I'd like to reuse input buffer to avoid useless IO."

Thanks,

Pramod

Hi Pramod.

Thank you for your quick reply.

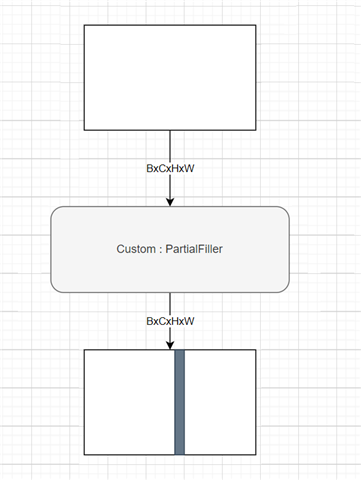

I have attached the figure for explaining how the custom layer works.

The PartialFiller layer set specific areas of input to zero for making input of next layer.

Can you explain why layer 3 is not overlapped?

I think if the in/out of the partialfiller layer is overlapped, it just update specific areas and it can avoid useless I/O as well.

Regards.

Dongwon Choi

OK Dongwon, Understood your concern. For now we don't have strict in-place adherence. For your example I can provide a workaround but not sure if this is your representative network. If you say so then I can provide some workaround

Hi Pramod.

If you give a workaround to us, I'll test it with my network.

Thanks

Hi Pramod.

Can I have workaround for this issue?

Please let me know if you ready to give it to me.

Regards

Dongwon Choi

Hi Dongwon Choi,

Please find the details as below

Option1

Since this is only insertion of pad values in a buffer, you can avoid custom layer approach and insert the padding as a function call towards the end of layer which produces this buffer

Option 2

File tidl_import_core.cpp, [Path: ti_dl\utils\tidlModelImport], please add below code before line "memcpy(orderedPerSimInfo, perSimInfo, sizeof(sPerfSim_t));"

{

/*--------------------------------------------------------------------*/

/* Modify the destination buffer address */

/* This change is only applicable for the especific network sahred */

/* if the network changes, then this change may not serve the purpose */

/*--------------------------------------------------------------------*/

int32_t layerExecIdx = 3 ;

int32_t layerDataInfoIdx = perSimInfo->layerExecutionOrder[layerExecIdx];

sBufferInfo_t *pSrcBuf = perSimInfo->sdataFlowInfo[layerDataInfoIdx].bufInfo[ IN_FEAT_MAP][ READ] ;

sBufferInfo_t *pDstBuf = perSimInfo->sdataFlowInfo[layerDataInfoIdx].bufInfo[OUT_FEAT_MAP][WRITE] ;

pDstBuf->baseMem = pSrcBuf->baseMem ;

}

Thanks,

With Regards,

Pramod

Hi Pramod.

I have tested it with option 2 workaround.

I have to fix code such as below because of compile error.

{

/*--------------------------------------------------------------------*/

/* Modify the destination buffer address */

/* This change is only applicable for the especific network sahred */

/* if the network changes, then this change may not serve the purpose */

/*--------------------------------------------------------------------*/

int32_t layerExecIdx = 4 ;

int32_t layerDataInfoIdx = perSimInfo->layerExecutionOrder[layerExecIdx];

sBufferInfo_t *pSrcBuf = &perSimInfo->sdataFlowInfo[layerDataInfoIdx].bufInfo[IN_FEAT_MAP][READ] ;

sBufferInfo_t *pDstBuf = &perSimInfo->sdataFlowInfo[layerDataInfoIdx].bufInfo[OUT_FEAT_MAP][WRITE] ;

pDstBuf->baseMem = pSrcBuf->baseMem ;

}

However, pDstBuf->baseMem and pSrcBuf->baseMem was already same before adding this code.

in/out address is still different.

Can you check this workaround at your side again?

Regards

Dongwon Choi

Hi

Do you have any updates?

I look forward to your prompt reply.

Regards

Dongwon Choi

Hi Dongwon Choi,

Are you trying the same network as shared earlier? Basically the network what you shared earlier was having layer 3 as custom layer and the request was to have same address for input and output for that particular layer but in above code I see that you have coded layerExecIdx = 4

In Layer 3, the 2 address highlighted as red are the source and destination address

------ 3( Custom) [3, 3] --[7 x 880 x 128] => [7 x 880 x 128] *** [7] ***[ COL] ***[0, 0, 112767, 112768]**** [7], [1],[7] -[2 ]---

MSMC, DMA, 1bfc0(114624), 1bf63(114531), 7( 7), c3f00( 802560), 372, 14f98e |||| L2, DMA, 1bfc0(114624), 1bfc0(114624), 2( 2), 37f80( 229248), 0, 0

NONE, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff ||||MSMC, CPU, 1bfc0(114624), 1bf63(114531), 7( 7), c3f00( 802560), 372, e

DDR, DMA, 0( 0), 0( 0), 54( 84), 0( 0), 0, 200480 |||| L2, DMA, 0( 0), 0( 0), 0( 0), 0( 0), 0, 37f80

L2, NA, 0( 0), 0( 0), 0( 0), 0( 0), 0, ffffffff

Padding Info [Row, Col]: Actual IN -> OUT : [ 1, 1] -> [ 1, 1], Required OUT : [ 1, 1], To fill zero OUT: [ 1, 1]

So please cross check the address observed in pDstBuf->baseMem and pSrcBuf->baseMem against the bufinfolog.txt. If you have changed the network then layerExecIdx has to be carefully point to the correct layer index

Hi Pramod

I have checked the workaround again, I found out it works that I expected.

Thank you for your support

Regards

Dongwon