Part Number: PROCESSOR-SDK-AM437X

Hello,

we have some trouble with devices we have delivered to our customers. Some customers have returned the device and complain a faulty behavior of the device.

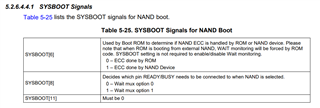

The setup of our device is AM437 processor. The processor boots from an external raw NAND flash. The board is a custom board which is very similar to the TI AM437 evaluation board. Our application is based on TI RTOS-Kernel SDK. Furthermore we use the TI PDK starterware SBL and we also use the starterware flashing utilities in our production line to flash the external NAND.

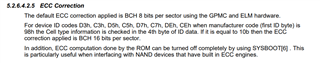

Further tests has shown that we have bit-flips on the NAND flash memory. I do not understand why there are bit-flips on the NAND. In my opinion the bootloader should correct these 1-Bit errors while reading the NAND pages of the application image thanks to the ECC. I have no idea why this is not working for us. I'm aware of the different reason for bit-flips and the meaning of bad blocks and bit errors.

As described before, we use the bootloader from TI PDK verion 1.0.9 starterware. We also use the TI flashing and booting utilities to flash the NAND in our production-line (also from the same PDK version). We expected the bad block management and ECC mechanism will work "out of the box" by this software components. Is this correct? But it seems like no ECC correction is used.

Can you give a detailed explanation how the bad block management and ECC mechanism will work within the SBL and the flashing utility TI starterware component?

Furthermore I'm a little bit confused about the flashing utility. After a code inspection of the nandwriter source code I assume that NAND vendor bad block information will not be evaluate by the source code and the used pages will initially erased which cause a irreversible deletion of the NAND vendor bad block information. This behavior does not correspond to the NAND vendor recommendations about initial bad block handling. Therefore we can not guarantee that we are using also blocks of the NAND which were marked as bad blocks from the NAND vendor. Am I right with my assumption, is this behavior of the flashing utility intended? If so why? Furthermore I'm not sure if the TI flashing utility is a tool which is intended for use in the production line for series production. Can you confirm that the usage in prodcution line is also intended? Or is it a better way to use other flashing utilities in production line?

Have you any idea why the ECC correction does not work for us?