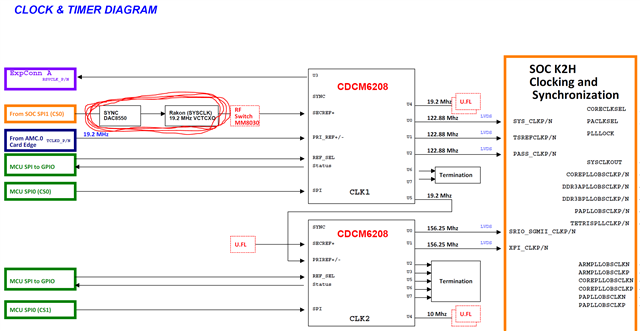

I'm using XTCIEVMK2X ver4.0 board and trying to do some experiments with PTP. I have PTPd successfully using my device driver that implements hardware time stamping (with CPTS module). Some functionality that I'm missing is adjust frequency capability. In a Keystone 2 "Time Synchronization" power point, there's mention that I should be able to do this by writing to DAC over SPI. I was hoping for more information about this (I'm not seeing anything about VCX0, DAC, or SPI in Keystone PLL user's guide). Also is there anywhere I could get reference driver and/or DPLL SW that's alluded to in that power point?