- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Device: TDA4

SDK Vesion: sdk7_03

mcu2_0 I2C works in master polling mode. The I2C waveform is as follows.

After mcu2_0 sends out the first byte, the slave device has given a response signal.

But the XRDY bit of the I2C_IRQSTATUS_RAW register is always 0, and mcu2_0 cannot send out the second byte of data.

Please give me some help. Thanks!

Is this on an EVM or your own board? If it's not an EVM, can you share the i2c schematics? Also, it's hard to know what's going on without seeing the registers. What values are you writing to the i2c registers before the transfer, and what are you doing to start the transfer? When you're in the polling XRDY state, can you dump all of the i2c registers? If you're using MCU_I2C0, that would be registers 0x40B00000 to 0x40B000D8.

Regards,

Zack

This is our own board. I2C slave device is max96722.The schematic of i2c is as follows. R4910 and R4911 are 0 ohms.

The i2c function I call is Board_i2c16BitRegWr in the Iss_sensors.c file,it hang at line 1036 of I2C_v1.c about 17 seconds because I2C_INT_TRANSMIT_READY is always 0, finally it's timeout.

The file iss_sensors.c and I2C_v1.c are in the attachment. All of the i2c registers dumped as follow

The attached file log0514.txt is the full log

[MCU2_0] 38.076217 s: register 0x02010000 is 0x80c

[MCU2_0] 38.076269 s: register 0x02010004 is 0x5040

[MCU2_0] 38.076308 s: register 0x02010008 is 0x0

[MCU2_0] 38.076344 s: register 0x0201000C is 0x0

[MCU2_0] 38.076378 s: register 0x02010010 is 0x214

[MCU2_0] 38.076416 s: register 0x02010014 is 0x0

[MCU2_0] 38.076467 s: register 0x02010018 is 0x0

[MCU2_0] 38.076504 s: register 0x0201001C is 0x0

[MCU2_0] 38.076539 s: register 0x02010020 is 0x0

[MCU2_0] 38.076574 s: register 0x02010024 is 0x5400

[MCU2_0] 38.076614 s: register 0x02010028 is 0x1400

[MCU2_0] 38.076650 s: register 0x0201002C is 0x0

[MCU2_0] 38.076687 s: register 0x02010030 is 0x0

[MCU2_0] 38.076723 s: register 0x02010034 is 0x6f6f

[MCU2_0] 38.076759 s: register 0x02010038 is 0x0

[MCU2_0] 38.076794 s: register 0x0201003C is 0x0

[MCU2_0] 38.076830 s: register 0x02010040 is 0x0

[MCU2_0] 38.076866 s: register 0x02010044 is 0x0

[MCU2_0] 38.076900 s: register 0x02010048 is 0x0

[MCU2_0] 38.076935 s: register 0x0201004C is 0x0

[MCU2_0] 38.076972 s: register 0x02010050 is 0x0

[MCU2_0] 38.077006 s: register 0x02010054 is 0x0

[MCU2_0] 38.077041 s: register 0x02010058 is 0x0

[MCU2_0] 38.077078 s: register 0x0201005C is 0x0

[MCU2_0] 38.077113 s: register 0x02010060 is 0x0

[MCU2_0] 38.077149 s: register 0x02010064 is 0x0

[MCU2_0] 38.077183 s: register 0x02010068 is 0x0

[MCU2_0] 38.077218 s: register 0x0201006C is 0x0

[MCU2_0] 38.077255 s: register 0x02010070 is 0x0

[MCU2_0] 38.077291 s: register 0x02010074 is 0x0

[MCU2_0] 38.077327 s: register 0x02010078 is 0x0

[MCU2_0] 38.077363 s: register 0x0201007C is 0x0

[MCU2_0] 38.077399 s: register 0x02010080 is 0x0

[MCU2_0] 38.077446 s: register 0x02010084 is 0x0

[MCU2_0] 38.077486 s: register 0x02010088 is 0x5400

[MCU2_0] 38.077524 s: register 0x0201008C is 0x0

[MCU2_0] 38.077563 s: register 0x02010090 is 0x1

[MCU2_0] 38.077597 s: register 0x02010094 is 0xf0f

[MCU2_0] 38.077632 s: register 0x02010098 is 0x3

[MCU2_0] 38.077669 s: register 0x0201009C is 0x3f

[MCU2_0] 38.077706 s: register 0x020100A0 is 0x0

[MCU2_0] 38.077742 s: register 0x020100A4 is 0x8600

[MCU2_0] 38.077779 s: register 0x020100A8 is 0x1

[MCU2_0] 38.077813 s: register 0x020100AC is 0x29

[MCU2_0] 38.077851 s: register 0x020100B0 is 0x7

[MCU2_0] 38.077884 s: register 0x020100B4 is 0x8

[MCU2_0] 38.077922 s: register 0x020100B8 is 0xa

[MCU2_0] 38.077960 s: register 0x020100BC is 0x4060

[MCU2_0] 38.077996 s: register 0x020100C0 is 0x8003

[MCU2_0] 38.078032 s: register 0x020100C4 is 0x0

[MCU2_0] 38.078069 s: register 0x020100C8 is 0x0

[MCU2_0] 38.078104 s: register 0x020100CC is 0x0

[MCU2_0] 38.078139 s: register 0x020100D0 is 0x0

[MCU2_0] 38.078174 s: register 0x020100D4 is 0x0

U-Boot SPL 2020.01-svn2210 (May 11 2021 - 10:51:16 +0800)

SYSFW ABI: 3.1 (firmware rev 0x0015 '21.1.1--v2021.01a (Terrific Lla')

Reading on-board EEPROM at 0x50 failed -1

Trying to boot from MMC2

Loading Environment from MMC... *** Warning - No MMC card found, using default environment

Starting ATF on ARM64 core...

NOTICE: BL31: v2.4(release):07.03.00.005-dirty

NOTICE: BL31: Built : 00:15:40, Apr 10 2021

U-Boot SPL 2020.01-svn2210 (May 12 2021 - 18:31:56 +0800)

SYSFW ABI: 3.1 (firmware rev 0x0015 '21.1.1--v2021.01a (Terrific Lla')

Reading on-board EEPROM at 0x50 failed -1

Trying to boot from MMC2

i2c_write: error waiting for data ACK (status=0x116)

Error reading output register

U-Boot 2020.01-svn2210 (May 12 2021 - 18:31:56 +0800)

SoC: J721E SR2.0

Model: Texas Instruments K3 J721E SoC

Reading on-board EEPROM at 0x50 failed -1

Board: J721EX-PM1-SOM rev E2

DRAM: 4 GiB

not found for dev hbmc-mux

Flash: 0 Bytes

MMC: sdhci@4f80000: 0, sdhci@4fb0000: 1

Loading Environment from MMC... *** Warning - bad CRC, using default environment

In: serial@2800000

Out: serial@2800000

Err: serial@2800000

Reading on-board EEPROM at 0x50 failed -1

Net: Could not get PHY for ethernet@46000000: addr 0

phy_connect() failed

No ethernet found.

Hit any key to stop autoboot: 0

i2c_write: error waiting for data ACK (status=0x116)

Error reading output register

switch to partitions #0, OK

mmc1 is current device

i2c_write: error waiting for data ACK (status=0x116)

Error reading output register

SD/MMC found on device 1

526 bytes read in 3 ms (170.9 KiB/s)

Loaded env from uEnv.txt

Importing environment from mmc1 ...

Running uenvcmd ...

Core 1 is already in use. No rproc commands work

Core 2 is already in use. No rproc commands work

22783504 bytes read in 941 ms (23.1 MiB/s)

Load Remote Processor 2 with data@addr=0x82000000 22783504 bytes: Success!

1968096 bytes read in 83 ms (22.6 MiB/s)

Load Remote Processor 3 with data@addr=0x82000000 1968096 bytes: Success!

1579120 bytes read in 67 ms (22.5 MiB/s)

Load Remote Processor 6 with data@addr=0x82000000 1579120 bytes: Success!

1579120 bytes read in 68 ms (22.1 MiB/s)

Load Remote Processor 7 with data@addr=0x82000000 1579120 bytes: Success!

10268600 bytes read in 425 ms (23 MiB/s)

Load Remote Processor 8 with data@addr=0x82000000 10268600 bytes: Success!

############################eth uart debug test########################

Enabling clocks!

[NIMU_NDK] ENET has been started successfully

8176820 bytes read in 341 ms (22.9 MiB/s)

## Starting application at 0x80080000 ...

MMU: 16-bit ASID 44-bit PA TCR_EL1=b5183519

cpu0: MPIDR=80000000

cpu0: MIDR=411fd080 Cortex-A72 r1p0

cpu0: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT

cpu0: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1

cpu0: L1 Icache 48K linesz=64 set/way=256/3

cpu0: L1 Dcache 32K linesz=64 set/way=256/2

cpu0: L2 Unified 1024K linesz=64 set/way=1024/16

Display set to R5

GPIO0_117 : 00200108

Loading IFS...decompressing...done

cpu1: MPIDR=80000001

cpu1: MIDR=411fd080 Cortex-A72 r1p0

cpu1: CWG=4 ERG=4 Dminline=4 Iminline=4 PIPT

cpu1: CLIDR=a200023 LoUU=1 LoC=2 LoUIS=1

cpu1: L1 Icache 48K linesz=64 set/way=256/3

cpu1: L1 Dcache 32K linesz=64 set/way=256/2

cpu1: L2 Unified 1024K linesz=64 set/way=1024/16

System page at phys:0000000080011000 user:ffffff8040254000 kern:ffffff8040251000

Starting next program at vffffff8060086e10

All ClockCycles offsets within tolerance

Welcome to QNX Neutrino 7.1.0 on the TI J721E EVM Board!!

Starting random service ...

start serial driver

Starting MMC/SD memory card driver... eMMC

Starting MMC/SD memory card driver... SD

Starting XHCI driver on USB3SS0 and USB3SS1

Path=0 - am65x

target=0 lun=0 Direct-Access(0) - SDMMC: 032GB4 Rev: 0.4

Setting environment variables...

done..

Mounting the sd ..

Looking for user script to run: /ti_fs/scripts/user.sh

Running user script...

user.sh called...

Setting additional environment variables...

Starting tisci-mgr..

Starting shmemallocator..

Starting tiipc-mgr..

Mailbox_plugInterrupt: interrupt Number 489, arg 0x36CCA018

Mailbox_plugInterrupt: interrupt Number 490, arg 0x36CCA1B8

Mailbox_plugInterrupt: interrupt Number 491, arg 0x36CCA358

Mailbox_plugInterrupt: interrupt Number 492, arg 0x36CCA4F8

Mailbox_plugInterrupt: interrupt Number 493, arg 0x36CCA698

Process 57360 (tiipc-mgr) terminated SIGSEGV code=1 fltno=11 ip=0000003536c8014c(/ti_fs/tibin/tiipc-mgr@lose+0x0000000000004dec) mapaddr=000000000001114c. ref=0000002300000184

Memory fault (core dumped)

Starting tiudma-mgr..

Start screen..

screen started with dss_on_r5 configuration..

done...

J7EVM@QNX:/#

J7EVM@QNX:/# /ti_fs/scripts/user.sh

user.sh called...

Setting additional environment variables...

Starting tisci-mgr..

tisci resmgr already running...: No error

Starting shmemallocator..

Starting tiipc-mgr..

Mailbox_plugInterrupt: interrupt Number 489, arg 0xD4A19018

Mailbox_plugInterrupt: interrupt Number 490, arg 0xD4A191B8

Mailbox_plugInterrupt: interrupt Number 491, arg 0xD4A19358

Mailbox_plugInterrupt: interrupt Number 492, arg 0xD4A194F8

Mailbox_plugInterrupt: interrupt Number 493, arg 0xD4A19698

Starting TI IPC Resmgr

Starting tiudma-mgr..

UDMA resmgr already running...: No error

Start screen..

Screen server is already running

screen started with dss_on_r5 configuration..

J7EVM@QNX:/# cd /ti_fs/vision_apps/

J7EVM@QNX:/ti_fs/vision_apps# ./vision_apps_init.sh

J7EVM@QNX:/ti_fs/vision_apps# [MCU1_0] 0.038218 s: CIO: Init ... Done !!!

[MCU1_0] 0.038293 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz>

[MCU1_0] 0.038336 s: APP: Init ... !!!

[MCU1_0] 0.038355 s: MEM: Init ... !!!

[MCU1_0] 0.038386 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e0000000 of size 8388608 bytes !!!

[MCU1_0] 0.038439 s: MEM: Init ... Done !!!

[MCU1_0] 0.038459 s: IPC: Init ... !!!

[MCU1_0] 0.038488 s: IPC: 7 CPUs participating in IPC !!!

[MCU1_0] 0.045353 s: IPC: Init ... Done !!!

[MCU1_0] 0.045417 s: APP: Syncing with 6 CPUs ... !!!

[MCU1_0] 5.128992 s: APP: Syncing with 6 CPUs ... Done !!!

[MCU1_0] 5.129221 s: REMOTE_SERVICE: Init ... !!!

[MCU1_0] 5.130888 s: REMOTE_SERVICE: Init ... Done !!!

[MCU1_0] 5.136566 s: APP: Init ... Done !!!

[MCU1_0] 5.137523 s: APP: Run ... !!!

[MCU1_0] 5.139598 s: IPC: Starting echo test ...

[MCU1_0] 5.144616 s: APP: Run ... Done !!!

[MCU1_0] 5.145821 s: IPC: Echo status: mpu1_0[x] mcu1_0[s] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[.] C7X_1[.]

[MCU1_0] 5.145925 s: IPC: Echo status: mpu1_0[x] mcu1_0[s] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[P] C7X_1[.]

[MCU1_0] 5.146003 s: IPC: Echo status: mpu1_0[x] mcu1_0[s] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[P] C7X_1[P]

[MCU1_0] 5.204112 s: IPC: Echo status: mpu1_0[x] mcu1_0[s] mcu2_0[x] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[P]

[MCU1_0] 5.358720 s: IPC: Echo status: mpu1_0[x] mcu1_0[s] mcu2_0[P] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[P]

[MCU2_0] 4.395373 s: CIO: Init ... Done !!!

[MCU2_0] 4.395438 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz>

[MCU2_0] 4.395478 s: APP: Init ... !!!

[MCU2_0] 4.395498 s: SCICLIENT: Init ... !!!

[MCU2_0] 4.395704 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[MCU2_0] 4.395739 s: SCICLIENT: DMSC FW revision 0x15

[MCU2_0] 4.395761 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU2_0] 4.395785 s: SCICLIENT: Init ... Done !!!

[MCU2_0] 4.395805 s: UDMA: Init ... !!!

[MCU2_0] 4.396952 s: UDMA: Init ... Done !!!

[MCU2_0] 4.397004 s: MEM: Init ... !!!

[MCU2_0] 4.397039 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e1000000 of size 16777216 bytes !!!

[MCU2_0] 4.397091 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000000) @ 3600000 of size 131072 bytes !!!

[MCU2_0] 4.397137 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000000) @ d8000000 of size 16777216 bytes !!!

[MCU2_0] 4.397181 s: MEM: Init ... Done !!!

[MCU2_0] 4.397200 s: IPC: Init ... !!!

[MCU2_0] 4.397227 s: IPC: 7 CPUs participating in IPC !!!

[MCU2_0] 4.403670 s: IPC: Init ... Done !!!

[MCU2_0] 4.403731 s: APP: Syncing with 6 CPUs ... !!!

[MCU2_0] 5.128991 s: APP: Syncing with 6 CPUs ... Done !!!

[MCU2_0] 5.129031 s: REMOTE_SERVICE: Init ... !!!

[MCU2_0] 5.130879 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_0] 5.130944 s: ETHFW: Init ... !!!

[MCU2_0] 5.224203 s: CPSW_9G Test on MAIN NAVSS

[MCU2_0] 5.236172 s: PHY 1 is alive

[MCU2_0] 5.237913 s: ETHFW: Version : 0.01.01

[MCU2_0] 5.237971 s: ETHFW: Build Date: May 11, 2021

[MCU2_0] 5.237999 s: ETHFW: Build Time: 17:54:31

[MCU2_0] 5.238022 s: ETHFW: Commit SHA:

[MCU2_0] 5.238045 s: ETHFW: Init ... DONE !!!

[MCU2_0] 5.238067 s: ETHFW: Remove server Init ... !!!

[MCU2_0] 5.239189 s: Remote demo device (core : mcu2_0) .....

[MCU2_0] 5.239243 s: ETHFW: Remove server Init ... DONE !!!

[MCU2_0] 5.245173 s: Host MAC address: 70:ff:76:1d:92:c2

[MCU2_0] 5.288449 s: FVID2: Init ... !!!

[MCU2_0] 5.288541 s: FVID2: Init ... Done !!!

[MCU2_0] 5.288581 s: DSS: Init ... !!!

[MCU2_0] 5.288604 s: DSS: Display type is eDP !!!

[MCU2_0] 5.288623 s: DSS: SoC init ... !!!

[MCU2_0] 5.288641 s: SCICLIENT: Sciclient_pmSetModuleState module=152 state=2

[MCU2_0] 5.288822 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.288851 s: SCICLIENT: Sciclient_pmSetModuleState module=297 state=2

[MCU2_0] 5.288997 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.289022 s: SCICLIENT: Sciclient_pmSetModuleState module=151 state=2

[MCU2_0] 5.289135 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.289160 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=9 parent=11

[MCU2_0] 5.289250 s: SCICLIENT: Sciclient_pmSetModuleClkParent success

[MCU2_0] 5.289276 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=13 parent=18

[MCU2_0] 5.289358 s: SCICLIENT: Sciclient_pmSetModuleClkParent success

[MCU2_0] 5.289388 s: SCICLIENT: Sciclient_pmSetModuleClkParent module=152 clk=1 parent=2

[MCU2_0] 5.289465 s: SCICLIENT: Sciclient_pmSetModuleClkParent success

[MCU2_0] 5.289501 s: SCICLIENT: Sciclient_pmSetModuleClkFreq module=152 clk=1 freq=148500000

[MCU2_0] 5.290478 s: SCICLIENT: Sciclient_pmSetModuleClkFreq success

[MCU2_0] 5.290510 s: SCICLIENT: Sciclient_pmModuleClkRequest module=152 clk=1 state=2 flag=0

[MCU2_0] 5.290637 s: SCICLIENT: Sciclient_pmModuleClkRequest success

[MCU2_0] 5.290664 s: DSS: SoC init ... Done !!!

[MCU2_0] 5.290683 s: DSS: Board init ... !!!

[MCU2_0] 5.290702 s: DSS: Turning on DP_PWR pin for eDP adapters ... !!!

[MCU2_0] 5.291009 s: DSS: Turning on DP_PWR pin for eDP adapters ... Done!!!

[MCU2_0] 5.291046 s: DSS: Board init ... Done !!!

[MCU2_0] 5.308996 s: DSS: Init ... Done !!!

[MCU2_0] 5.309053 s: VHWA: VPAC Init ... !!!

[MCU2_0] 5.309075 s: SCICLIENT: Sciclient_pmSetModuleState module=290 state=2

[MCU2_0] 5.309237 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.309267 s: VHWA: LDC Init ... !!!

[MCU2_0] 5.312384 s: VHWA: LDC Init ... Done !!!

[MCU2_0] 5.312461 s: VHWA: MSC Init ... !!!

[MCU2_0] 5.321464 s: VHWA: MSC Init ... Done !!!

[MCU2_0] 5.321516 s: VHWA: NF Init ... !!!

[MCU2_0] 5.323082 s: VHWA: NF Init ... Done !!!

[MCU2_0] 5.323133 s: VHWA: VISS Init ... !!!

[MCU2_0] 5.329532 s: VHWA: VISS Init ... Done !!!

[MCU2_0] 5.329583 s: VHWA: VPAC Init ... Done !!!

[MCU2_0] 5.329621 s: VX_ZONE_INIT:Enabled

[MCU2_0] 5.329643 s: VX_ZONE_ERROR:Enabled

[MCU2_0] 5.329662 s: VX_ZONE_WARNING:Enabled

[MCU2_0] 5.330703 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target IPU1-0

[MCU2_0] 5.330967 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_NF

[MCU2_0] 5.331211 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_LDC1

[MCU2_0] 5.331498 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_MSC1

[MCU2_0] 5.331754 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_MSC2

[MCU2_0] 5.332023 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VPAC_VISS1

[MCU2_0] 5.332296 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE1

[MCU2_0] 5.332631 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE2

[MCU2_0] 5.332913 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DISPLAY1

[MCU2_0] 5.333182 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DISPLAY2

[MCU2_0] 5.333469 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CSITX

[MCU2_0] 5.333755 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE3

[MCU2_0] 5.334043 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE4

[MCU2_0] 5.334316 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE5

[MCU2_0] 5.334630 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE6

[MCU2_0] 5.334922 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE7

[MCU2_0] 5.335201 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAPTURE8

[MCU2_0] 5.335496 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target MCAN0

[MCU2_0] 5.335763 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target MCAN3

[MCU2_0] 5.336019 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target MCAN7

[MCU2_0] 5.336265 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target MCAN9

[MCU2_0] 5.336560 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target CAMERASWITCH

[MCU2_0] 5.336613 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[MCU2_0] 5.336641 s: APP: OpenVX Target kernel init ... !!!

[MCU2_0] 5.347953 s: APP: tivxRegisterCameraSwitchTargetR5FKernels !!!

[MCU2_0] 5.348004 s: Start to call tivxAddTargetKernelCameraSwitch

[MCU2_0] 5.348033 s: Start to call tivxAddTargetKernelCameraSwitch 6

[MCU2_0] 5.348062 s: Start to call tivxAddTargetKernelCameraSwitch CAMERASWITCH

[MCU2_0] 5.348106 s: APP: OpenVX Target kernel init ... Done !!!

[MCU2_0] 5.348132 s: CSI2RX: Init ... !!!

[MCU2_0] 5.348148 s: SCICLIENT: Sciclient_pmSetModuleState module=25 state=2

[MCU2_0] 5.348250 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.348277 s: SCICLIENT: Sciclient_pmSetModuleState module=26 state=2

[MCU2_0] 5.348389 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.348414 s: SCICLIENT: Sciclient_pmSetModuleState module=27 state=2

[MCU2_0] 5.348549 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.348578 s: SCICLIENT: Sciclient_pmSetModuleState module=147 state=2

[MCU2_0] 5.348659 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.348684 s: SCICLIENT: Sciclient_pmSetModuleState module=148 state=2

[MCU2_0] 5.348756 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.349485 s: CSI2RX: Init ... Done !!!

[MCU2_0] 5.349534 s: CSI2TX: Init ... !!!

[MCU2_0] 5.349557 s: SCICLIENT: Sciclient_pmSetModuleState module=25 state=2

[MCU2_0] 5.349640 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.349668 s: SCICLIENT: Sciclient_pmSetModuleState module=28 state=2

[MCU2_0] 5.349772 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.349797 s: SCICLIENT: Sciclient_pmSetModuleState module=296 state=2

[MCU2_0] 5.349884 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_0] 5.350405 s: CSI2TX: Init ... Done !!!

[MCU2_0] 5.350483 s: ISS: Init ... !!!

[MCU2_0] 5.350510 s: IssSensor_Init start

[MCU2_0] 5.350534 s: Found sensor IMX390-UB953_D3 at location 0

[MCU2_0] 5.350566 s: Found sensor AR0233-UB953_MARS at location 1

[MCU2_0] 5.350595 s: Found sensor AR0820-UB953_LI at location 2

[MCU2_0] 5.350624 s: Found sensor UB9xxx_RAW12_TESTPATTERN at location 3

[MCU2_0] 5.350652 s: Found sensor UB96x_UYVY_TESTPATTERN at location 4

[MCU2_0] 5.350679 s: Found sensor GW_AR0233_UYVY at location 5

[MCU2_0] 5.350705 s: Found sensor MAX96722_MAX96717_OX03C10 at location 6

[MCU2_0] 5.350732 s: IssSensor_Init end

[MCU2_0] 5.350750 s: IssSensor_Init ... Done !!!

[MCU2_0] 5.350820 s: vissRemoteServer_Init ... Done !!!

[MCU2_0] 5.350872 s: IttRemoteServer_Init ... Done !!!

[MCU2_0] 5.350899 s: UDMA Copy: Init ... !!!

[MCU2_0] 5.352482 s: UDMA Copy: Init ... Done !!!

[MCU2_0] 5.352535 s: APP: Camera GPIO Set start !!!

[MCU2_0] 5.352599 s: APP: Init ... Done !!!

[MCU2_0] 5.352624 s: APP: Run ... !!!

[MCU2_0] 5.352644 s: IPC: Starting echo test ...

[MCU2_0] 5.355182 s: APP: Run ... Done !!!

[MCU2_0] 5.355531 s: BOARD: GPIO CFG !!!

[MCU2_0] 5.359034 s: IPC: Echo status: mpu1_0[x] mcu1_0[.] mcu2_0[s] mcu2_1[.] C66X_1[P] C66X_2[.] C7X_1[.]

[MCU2_0] 5.359203 s: IPC: Echo status: mpu1_0[x] mcu1_0[.] mcu2_0[s] mcu2_1[.] C66X_1[P] C66X_2[P] C7X_1[.]

[MCU2_0] 5.359330 s: IPC: Echo status: mpu1_0[x] mcu1_0[.] mcu2_0[s] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[.]

[MCU2_0] 5.359478 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[s] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[.]

[MCU2_0] 5.359603 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[s] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[P]

[MCU2_1] 4.493366 s: CIO: Init ... Done !!!

[MCU2_1] 4.493436 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz>

[MCU2_1] 4.493479 s: APP: Init ... !!!

[MCU2_1] 4.493500 s: SCICLIENT: Init ... !!!

[MCU2_1] 4.493709 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[MCU2_1] 4.493743 s: SCICLIENT: DMSC FW revision 0x15

[MCU2_1] 4.493765 s: SCICLIENT: DMSC FW ABI revision 3.1

[MCU2_1] 4.493789 s: SCICLIENT: Init ... Done !!!

[MCU2_1] 4.493810 s: UDMA: Init ... !!!

[MCU2_1] 4.495089 s: UDMA: Init ... Done !!!

[MCU2_1] 4.495139 s: MEM: Init ... !!!

[MCU2_1] 4.495171 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e2000000 of size 16777216 bytes !!!

[MCU2_1] 4.495223 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 3620000 of size 131072 bytes !!!

[MCU2_1] 4.495271 s: MEM: Created heap (DDR_NON_CACHE_ME, id=5, flags=0x00000000) @ d9000000 of size 117440512 bytes !!!

[MCU2_1] 4.495317 s: MEM: Init ... Done !!!

[MCU2_1] 4.495339 s: IPC: Init ... !!!

[MCU2_1] 4.495368 s: IPC: 7 CPUs participating in IPC !!!

[MCU2_1] 4.501618 s: IPC: Init ... Done !!!

[MCU2_1] 4.501674 s: APP: Syncing with 6 CPUs ... !!!

[MCU2_1] 5.128990 s: APP: Syncing with 6 CPUs ... Done !!!

[MCU2_1] 5.129026 s: REMOTE_SERVICE: Init ... !!!

[MCU2_1] 5.130706 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_1] 5.130769 s: FVID2: Init ... !!!

[MCU2_1] 5.130839 s: FVID2: Init ... Done !!!

[MCU2_1] 5.130866 s: VHWA: DMPAC: Init ... !!!

[MCU2_1] 5.130887 s: SCICLIENT: Sciclient_pmSetModuleState module=48 state=2

[MCU2_1] 5.131120 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_1] 5.131151 s: SCICLIENT: Sciclient_pmSetModuleState module=305 state=2

[MCU2_1] 5.131631 s: SCICLIENT: Sciclient_pmSetModuleState success

[MCU2_1] 5.131665 s: VHWA: DOF Init ... !!!

[MCU2_1] 5.139628 s: VHWA: DOF Init ... Done !!!

[MCU2_1] 5.139682 s: VHWA: SDE Init ... !!!

[MCU2_1] 5.142141 s: VHWA: SDE Init ... Done !!!

[MCU2_1] 5.142189 s: VHWA: DMPAC: Init ... Done !!!

[MCU2_1] 5.142215 s: VHWA: Codec: Init ... !!!

[MCU2_1] 5.142235 s: VHWA: VDEC Init ... !!!

[MCU2_1] 5.155563 s: VHWA: VDEC Init ... Done !!!

[MCU2_1] 5.155609 s: VHWA: VENC Init ... !!!

[MCU2_1] 5.155849 s: MM_ENC_Init: No OCM RAM pool available, fallback to DDR mode for above mp params

[MCU2_1] 5.195924 s: VHWA: VENC Init ... Done !!!

[MCU2_1] 5.195975 s: VHWA: Init ... Done !!!

[MCU2_1] 5.196012 s: VX_ZONE_INIT:Enabled

[MCU2_1] 5.196035 s: VX_ZONE_ERROR:Enabled

[MCU2_1] 5.196054 s: VX_ZONE_WARNING:Enabled

[MCU2_1] 5.197027 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DMPAC_SDE

[MCU2_1] 5.197249 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target DMPAC_DOF

[MCU2_1] 5.197501 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VDEC1

[MCU2_1] 5.197718 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VDEC2

[MCU2_1] 5.197926 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VENC1

[MCU2_1] 5.198135 s: VX_ZONE_INIT:[tivxPlatformCreateTargetId:55] Added target VENC2

[MCU2_1] 5.198185 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[MCU2_1] 5.198213 s: APP: OpenVX Target kernel init ... !!!

[MCU2_1] 5.198611 s: APP: OpenVX Target kernel init ... Done !!!

[MCU2_1] 5.198653 s: UDMA Copy: Init ... !!!

[MCU2_1] 5.200276 s: UDMA Copy: Init ... Done !!!

[MCU2_1] 5.200327 s: APP: Init ... Done !!!

[MCU2_1] 5.200350 s: APP: Run ... !!!

[MCU2_1] 5.200369 s: IPC: Starting echo test ...

[MCU2_1] 5.202737 s: APP: Run ... Done !!!

[MCU2_1] 5.204086 s: IPC: Echo status: mpu1_0[x] mcu1_0[.] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[.] C7X_1[.]

[MCU2_1] 5.204180 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[.] C7X_1[.]

[MCU2_1] 5.204251 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[.]

[MCU2_1] 5.204315 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[P]

[MCU2_1] 5.358668 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[P] mcu2_1[s] C66X_1[P] C66X_2[P] C7X_1[P]

[C6x_1 ] 4.594455 s: CIO: Init ... Done !!!

[C6x_1 ] 4.594489 s: ### CPU Frequency <ORG = 1350000000 Hz>, <NEW = 1350000000 Hz>

[C6x_1 ] 4.594502 s: APP: Init ... !!!

[C6x_1 ] 4.594509 s: SCICLIENT: Init ... !!!

[C6x_1 ] 4.594699 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[C6x_1 ] 4.594710 s: SCICLIENT: DMSC FW revision 0x15

[C6x_1 ] 4.594719 s: SCICLIENT: DMSC FW ABI revision 3.1

[C6x_1 ] 4.594729 s: SCICLIENT: Init ... Done !!!

[C6x_1 ] 4.594738 s: UDMA: Init ... !!!

[C6x_1 ] 4.596087 s: UDMA: Init ... Done !!!

[C6x_1 ] 4.596110 s: MEM: Init ... !!!

[C6x_1 ] 4.596123 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e4000000 of size 16777216 bytes !!!

[C6x_1 ] 4.596139 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 800000 of size 229376 bytes !!!

[C6x_1 ] 4.596154 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ e5000000 of size 50331648 bytes !!!

[C6x_1 ] 4.596170 s: MEM: Init ... Done !!!

[C6x_1 ] 4.596178 s: IPC: Init ... !!!

[C6x_1 ] 4.596191 s: IPC: 7 CPUs participating in IPC !!!

[C6x_1 ] 4.599781 s: IPC: Init ... Done !!!

[C6x_1 ] 4.599811 s: APP: Syncing with 6 CPUs ... !!!

[C6x_1 ] 5.128988 s: APP: Syncing with 6 CPUs ... Done !!!

[C6x_1 ] 5.128998 s: REMOTE_SERVICE: Init ... !!!

[C6x_1 ] 5.129782 s: REMOTE_SERVICE: Init ... Done !!!

[C6x_1 ] 5.129820 s: VX_ZONE_INIT:Enabled

[C6x_1 ] 5.129830 s: VX_ZONE_ERROR:Enabled

[C6x_1 ] 5.129838 s: VX_ZONE_WARNING:Enabled

[C6x_1 ] 5.130727 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[C6x_1 ] 5.130746 s: APP: OpenVX Target kernel init ... !!!

[C6x_1 ] 5.131027 s: APP: OpenVX Target kernel init ... Done !!!

[C6x_1 ] 5.131049 s: UDMA Copy: Init ... !!!

[C6x_1 ] 5.134667 s: UDMA Copy: Init ... Done !!!

[C6x_1 ] 5.134687 s: APP: Init ... Done !!!

[C6x_1 ] 5.135424 s: APP: Run ... !!!

[C6x_1 ] 5.135432 s: IPC: Starting echo test ...

[C6x_1 ] 5.136806 s: APP: Run ... Done !!!

[C6x_1 ] 5.137162 s: IPC: Echo status: mpu1_0[x] mcu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[s] C66X_2[P] C7X_1[.]

[C6x_1 ] 5.137200 s: IPC: Echo status: mpu1_0[x] mcu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_1 ] 5.145606 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[x] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_1 ] 5.203783 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[P] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_1 ] 5.358550 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[P] mcu2_1[P] C66X_1[s] C66X_2[P] C7X_1[P]

[C6x_2 ] 4.676456 s: CIO: Init ... Done !!!

[C6x_2 ] 4.676490 s: ### CPU Frequency <ORG = 1350000000 Hz>, <NEW = 1350000000 Hz>

[C6x_2 ] 4.676503 s: APP: Init ... !!!

[C6x_2 ] 4.676511 s: SCICLIENT: Init ... !!!

[C6x_2 ] 4.676712 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[C6x_2 ] 4.676723 s: SCICLIENT: DMSC FW revision 0x15

[C6x_2 ] 4.676732 s: SCICLIENT: DMSC FW ABI revision 3.1

[C6x_2 ] 4.676741 s: SCICLIENT: Init ... Done !!!

[C6x_2 ] 4.676750 s: UDMA: Init ... !!!

[C6x_2 ] 4.678094 s: UDMA: Init ... Done !!!

[C6x_2 ] 4.678118 s: MEM: Init ... !!!

[C6x_2 ] 4.678130 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ e8000000 of size 16777216 bytes !!!

[C6x_2 ] 4.678147 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 800000 of size 229376 bytes !!!

[C6x_2 ] 4.678161 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ e9000000 of size 50331648 bytes !!!

[C6x_2 ] 4.678177 s: MEM: Init ... Done !!!

[C6x_2 ] 4.678185 s: IPC: Init ... !!!

[C6x_2 ] 4.678199 s: IPC: 7 CPUs participating in IPC !!!

[C6x_2 ] 4.681784 s: IPC: Init ... Done !!!

[C6x_2 ] 4.681814 s: APP: Syncing with 6 CPUs ... !!!

[C6x_2 ] 5.128988 s: APP: Syncing with 6 CPUs ... Done !!!

[C6x_2 ] 5.128999 s: REMOTE_SERVICE: Init ... !!!

[C6x_2 ] 5.129775 s: REMOTE_SERVICE: Init ... Done !!!

[C6x_2 ] 5.129814 s: VX_ZONE_INIT:Enabled

[C6x_2 ] 5.129824 s: VX_ZONE_ERROR:Enabled

[C6x_2 ] 5.129833 s: VX_ZONE_WARNING:Enabled

[C6x_2 ] 5.130709 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[C6x_2 ] 5.130728 s: APP: OpenVX Target kernel init ... !!!

[C6x_2 ] 5.131019 s: APP: OpenVX Target kernel init ... Done !!!

[C6x_2 ] 5.131038 s: UDMA Copy: Init ... !!!

[C6x_2 ] 5.134377 s: UDMA Copy: Init ... Done !!!

[C6x_2 ] 5.134395 s: APP: Init ... Done !!!

[C6x_2 ] 5.135121 s: APP: Run ... !!!

[C6x_2 ] 5.135131 s: IPC: Starting echo test ...

[C6x_2 ] 5.136393 s: APP: Run ... Done !!!

[C6x_2 ] 5.136742 s: IPC: Echo status: mpu1_0[x] mcu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[x] C66X_2[s] C7X_1[P]

[C6x_2 ] 5.137173 s: IPC: Echo status: mpu1_0[x] mcu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[s] C7X_1[P]

[C6x_2 ] 5.145626 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[s] C7X_1[P]

[C6x_2 ] 5.203802 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[P] C66X_1[P] C66X_2[s] C7X_1[P]

[C6x_2 ] 5.358600 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[P] mcu2_1[P] C66X_1[P] C66X_2[s] C7X_1[P]

[C7x_1 ] 5.125462 s: CIO: Init ... Done !!!

[C7x_1 ] 5.125485 s: ### CPU Frequency <ORG = 1000000000 Hz>, <NEW = 1000000000 Hz>

[C7x_1 ] 5.125501 s: APP: Init ... !!!

[C7x_1 ] 5.125508 s: SCICLIENT: Init ... !!!

[C7x_1 ] 5.125690 s: SCICLIENT: DMSC FW version [21.1.1--v2021.01a (Terrific Lla]

[C7x_1 ] 5.125703 s: SCICLIENT: DMSC FW revision 0x15

[C7x_1 ] 5.125714 s: SCICLIENT: DMSC FW ABI revision 3.1

[C7x_1 ] 5.125725 s: SCICLIENT: Init ... Done !!!

[C7x_1 ] 5.125734 s: UDMA: Init ... !!!

[C7x_1 ] 5.126755 s: UDMA: Init ... Done !!!

[C7x_1 ] 5.126768 s: MEM: Init ... !!!

[C7x_1 ] 5.126779 s: MEM: Created heap (DDR_SHARED_MEM, id=0, flags=0x00000004) @ 100000000 of size 1073741824 bytes !!!

[C7x_1 ] 5.126801 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000001) @ 70020000 of size 8159232 bytes !!!

[C7x_1 ] 5.126818 s: MEM: Created heap (L2_MEM, id=2, flags=0x00000001) @ 64800000 of size 491520 bytes !!!

[C7x_1 ] 5.126835 s: MEM: Created heap (L1_MEM, id=3, flags=0x00000001) @ 64e00000 of size 16384 bytes !!!

[C7x_1 ] 5.126853 s: MEM: Created heap (DDR_SCRATCH_MEM, id=4, flags=0x00000001) @ ec000000 of size 268435456 bytes !!!

[C7x_1 ] 5.126871 s: MEM: Init ... Done !!!

[C7x_1 ] 5.126879 s: IPC: Init ... !!!

[C7x_1 ] 5.126889 s: IPC: 7 CPUs participating in IPC !!!

[C7x_1 ] 5.128959 s: IPC: Init ... Done !!!

[C7x_1 ] 5.128974 s: APP: Syncing with 6 CPUs ... !!!

[C7x_1 ] 5.128988 s: APP: Syncing with 6 CPUs ... Done !!!

[C7x_1 ] 5.128999 s: REMOTE_SERVICE: Init ... !!!

[C7x_1 ] 5.129346 s: REMOTE_SERVICE: Init ... Done !!!

[C7x_1 ] 5.129369 s: VX_ZONE_INIT:Enabled

[C7x_1 ] 5.129410 s: VX_ZONE_ERROR:Enabled

[C7x_1 ] 5.129421 s: VX_ZONE_WARNING:Enabled

[C7x_1 ] 5.129702 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

[C7x_1 ] 5.129717 s: APP: OpenVX Target kernel init ... !!!

[C7x_1 ] 5.129810 s: APP: OpenVX Target kernel init ... Done !!!

[C7x_1 ] 5.129825 s: APP: Init ... Done !!!

[C7x_1 ] 5.129833 s: APP: Run ... !!!

[C7x_1 ] 5.129842 s: IPC: Starting echo test ...

[C7x_1 ] 5.130404 s: APP: Run ... Done !!!

[C7x_1 ] 5.136727 s: IPC: Echo status: mpu1_0[x] mcu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[x] C66X_2[P] C7X_1[s]

[C7x_1 ] 5.137162 s: IPC: Echo status: mpu1_0[x] mcu1_0[x] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[P] C7X_1[s]

[C7x_1 ] 5.145645 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[x] C66X_1[P] C66X_2[P] C7X_1[s]

[C7x_1 ] 5.203817 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[x] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[s]

[C7x_1 ] 5.358622 s: IPC: Echo status: mpu1_0[x] mcu1_0[P] mcu2_0[P] mcu2_1[P] C66X_1[P] C66X_2[P] C7X_1[s]

J7EVM@QNX:/ti_fs/vision_apps# ./vx_app_single_cam.out

APP: Init QNX ... !!!

Sciclient_qnxVirtToPhyFxn:Error from mem_offset

Sciclient_qnxVirtToPhyFxn:Error from mem_offset

appIpcInit: IPC: Init QNX ... !!!

appIpcInit: IPC: Init ... Done !!!

21.397839 s: REMOTE_SERVICE: Init ... !!!

21.397983 s: REMOTE_SERVICE: Init ... Done !!!

21.398010 s: GTC Frequency = 200 MHz

APP: Init ... Done !!!

21.398034 s: VX_ZONE_INIT:Enabled

21.398048 s: VX_ZONE_ERROR:Enabled

21.398061 s: VX_ZONE_WARNING:Enabled

21.398258 s: VX_ZONE_INIT:[tivxInit:71] Initialization Done !!!

21.398293 s: VX_ZONE_INIT:[tivxHostInit:48] Initialization Done for HOST !!!

Single Camera Demo - (c) Texas Instruments 2019

========================================================

Usage,

./vx_app_single_cam.out --cfg <config file>

Defaulting to interactive mode

tivxImagingLoadKernels done

21.399086 s: ISS: Enumerating sensors ... !!!

[MCU2_0] 21.399191 s: ImageSensor_RemoteServiceHandler: IM_SENSOR_CMD_CREATE

[MCU2_0] 21.399329 s:

[MCU2_0] 21.399372 s: I2C: Object created 0x2010000

[MCU2_0] 21.399406 s: MAX96722 config start

[MCU2_0] 21.399469 s:

[MCU2_0] 21.399513 s: I2C:(0x2010000) Starting transaction to slave: 0x29

[MCU2_0] 38.076217 s: register 0x02010000 is 0x80c

[MCU2_0] 38.076269 s: register 0x02010004 is 0x5040

[MCU2_0] 38.076308 s: register 0x02010008 is 0x0

[MCU2_0] 38.076344 s: register 0x0201000C is 0x0

[MCU2_0] 38.076378 s: register 0x02010010 is 0x214

[MCU2_0] 38.076416 s: register 0x02010014 is 0x0

[MCU2_0] 38.076467 s: register 0x02010018 is 0x0

[MCU2_0] 38.076504 s: register 0x0201001C is 0x0

[MCU2_0] 38.076539 s: register 0x02010020 is 0x0

[MCU2_0] 38.076574 s: register 0x02010024 is 0x5400

[MCU2_0] 38.076614 s: register 0x02010028 is 0x1400

[MCU2_0] 38.076650 s: register 0x0201002C is 0x0

[MCU2_0] 38.076687 s: register 0x02010030 is 0x0

[MCU2_0] 38.076723 s: register 0x02010034 is 0x6f6f

[MCU2_0] 38.076759 s: register 0x02010038 is 0x0

[MCU2_0] 38.076794 s: register 0x0201003C is 0x0

[MCU2_0] 38.076830 s: register 0x02010040 is 0x0

[MCU2_0] 38.076866 s: register 0x02010044 is 0x0

[MCU2_0] 38.076900 s: register 0x02010048 is 0x0

[MCU2_0] 38.076935 s: register 0x0201004C is 0x0

[MCU2_0] 38.076972 s: register 0x02010050 is 0x0

[MCU2_0] 38.077006 s: register 0x02010054 is 0x0

[MCU2_0] 38.077041 s: register 0x02010058 is 0x0

[MCU2_0] 38.077078 s: register 0x0201005C is 0x0

[MCU2_0] 38.077113 s: register 0x02010060 is 0x0

[MCU2_0] 38.077149 s: register 0x02010064 is 0x0

[MCU2_0] 38.077183 s: register 0x02010068 is 0x0

[MCU2_0] 38.077218 s: register 0x0201006C is 0x0

[MCU2_0] 38.077255 s: register 0x02010070 is 0x0

[MCU2_0] 38.077291 s: register 0x02010074 is 0x0

[MCU2_0] 38.077327 s: register 0x02010078 is 0x0

[MCU2_0] 38.077363 s: register 0x0201007C is 0x0

[MCU2_0] 38.077399 s: register 0x02010080 is 0x0

[MCU2_0] 38.077446 s: register 0x02010084 is 0x0

[MCU2_0] 38.077486 s: register 0x02010088 is 0x5400

[MCU2_0] 38.077524 s: register 0x0201008C is 0x0

[MCU2_0] 38.077563 s: register 0x02010090 is 0x1

[MCU2_0] 38.077597 s: register 0x02010094 is 0xf0f

[MCU2_0] 38.077632 s: register 0x02010098 is 0x3

[MCU2_0] 38.077669 s: register 0x0201009C is 0x3f

[MCU2_0] 38.077706 s: register 0x020100A0 is 0x0

[MCU2_0] 38.077742 s: register 0x020100A4 is 0x8600

[MCU2_0] 38.077779 s: register 0x020100A8 is 0x1

[MCU2_0] 38.077813 s: register 0x020100AC is 0x29

[MCU2_0] 38.077851 s: register 0x020100B0 is 0x7

[MCU2_0] 38.077884 s: register 0x020100B4 is 0x8

[MCU2_0] 38.077922 s: register 0x020100B8 is 0xa

[MCU2_0] 38.077960 s: register 0x020100BC is 0x4060

[MCU2_0] 38.077996 s: register 0x020100C0 is 0x8003

[MCU2_0] 38.078032 s: register 0x020100C4 is 0x0

[MCU2_0] 38.078069 s: register 0x020100C8 is 0x0

[MCU2_0] 38.078104 s: register 0x020100CC is 0x0

[MCU2_0] 38.078139 s: register 0x020100D0 is 0x0

[MCU2_0] 38.078174 s: register 0x020100D4 is 0x0

[MCU2_0] 38.078223 s: Error writing 0x75 to MAX96722 register 0x13

[MCU2_0] 38.078270 s: MAX96722 Error: Reg Write Failed for regAddr 13

[MCU2_0] 38.078300 s: End of MAX96722 config

[MCU2_0] 38.078344 s: Error : max96722_cfgScript returned -1 while configuring DES 0

38.078526 s: ISS: ERROR: Enumerating sensors failed !!!

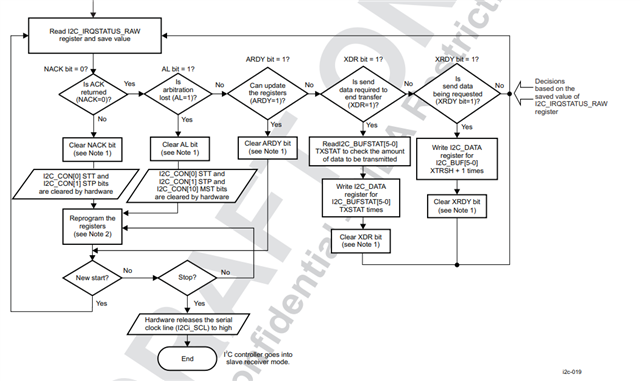

Select camera port index 0-7 :Based on this flowchart from the TRM:

You should be first polling the XDR bit (which is 1 according to your register dump). This means that you need to write to I2C_DATA 3 times.

Based on my reading of the TRM, I agree that the XRDY bit should be set as well, since the TX FIFO is empty. But the behavior seems to be that if the number of bytes left in the transfer is less than the threshold amount, then only XDR will be set. I would try the following two fixes:

Add some logic to your code which first polls XDR and handles the XDR=1 situation accordingly.

OR

Try changing your threshold to 1.

Regards,

Zack

Thank you for your reply.

The current threshold of 16 is an error value. After I changed the threshold to 1, it can work well