Hi

There's a question about RESET circuit. Please answer to question.

1. Is there any problem that is expected when simplified with POWER-ON and Cold RESET as above circuit?

Thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi

There's a question about RESET circuit. Please answer to question.

1. Is there any problem that is expected when simplified with POWER-ON and Cold RESET as above circuit?

Thanks.

HI JJD

I have a further question.

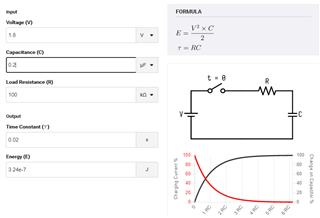

1. Is it a problem because the RC value in the picture above is Reset time=1ms? (If 10Kohm ->100Kohm, 100nF ->220nF is changed and the reset time = 20ms, is it appropriate?)

2. Is the reset circuit using RC inappropriate?

Thanks for your kind answer

Yes, there are several requirements outlined in the datasheet for MCU_PORz. The signal needs to be low throughout the power on sequencing and remain low for some time after all power supplies are stable, as detailed in figure 7-3 in the datasheet. Typically, this signal is a delayed output of some power good circuitry from a PMIC or voltage supervisor (you can see an example of this in the GP EVM). There is also input slew rate requirement which the RC circuit may not be able to meet across temp.

Regards,

James