Part Number: TDA4VM

Enabling inline ECC for memory size <= 2GB is simpler as the memory address range is with in 32 bit address(0x80000000. - 0xFFFFFFFF)

How to enable Inline ECC > 2GB address.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

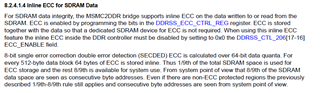

Snapshot from TRM:

ECC enabling needs to be done at the time of DDR initialization. In the Linux boot flow the DDR configuration is done by R5 SPL.

R5 is a 32-bit processor. Hence it can not access addresses that need > 32 bits.

This can be over come by utilizing the RAT - Region based address translator for MCU R5F.

The RAT converts the > 32 bit addresses to 32 bit address & helps R5F access memory regions with > 32 bit address

The below patch enables ECC for 3GB.

So While DDR gets initialized we map 0x80000000(Accessible by R5) to 0x880000000 (> 32 bits).

Clear them out to 0s. Unmap the RAT translation.

Set the ECC second range for the 3rd GB.

Boot tested with Linux and memtester runs well.

The patch is on top of SDK7.3 U-Boot.

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/791/ECC_2D00_for_2D00_3_2D00_GB.patch

cd $PSDKLA_7.3/board-support/u-boot* git am ECC-for-3-GB.patch cd ../.. make u-boot cp board-support/u-boot_build/r5/tiboot3.bin board-support/u-boot_build/a72/tispl.bin board-support/u-boot_build/a72/u-boot.img board-support/prebuilt-binaries/sysfw.itb /media/$USER/boot sync

Note: Enabling ECC will add to boot time at R5 SPL.

Best Regards,

Keerthy