Part Number: DRA821U

Other Parts Discussed in Thread: DRA821

Dear support,

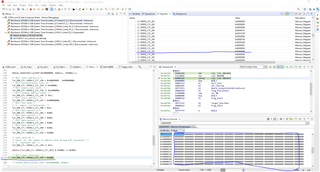

For DDR ECC per-load, we use the BIST engine for SDRAM initilization, but it fails, the following is the registers configured,

Could you help me check whether the configuration is Ok?

I want to initialize the 0x9000 0000 ~ 0x9000 03FF(1KB)

/* BIST start address 0.*/

Tst_DDR_CTL->DENALI_CTL_196 = 0x90000000;

/* BIST start address 1.*/

Tst_DDR_CTL->DENALI_CTL_197 = 0x00000000;

/* BIST test mode.*/

/* 4 - memory initialization. */

Tst_DDR_CTL->DENALI_CTL_200 = 0x4;

/* BIST data pattern 0.*/

Tst_DDR_CTL->DENALI_CTL_201 = 0x55AA55AA;

/* BIST data pattern 1.*/

Tst_DDR_CTL->DENALI_CTL_202 = 0x55AA55AA;

/* BIST data pattern 2.*/

Tst_DDR_CTL->DENALI_CTL_203 = 0x55AA55AA;

/* BIST data pattern 3.*/

Tst_DDR_CTL->DENALI_CTL_204 = 0x55AA55AA;

/* bit0 -BIST GO */

/* bit18 -21, the number of address bits during BIST operation. */

/* 9 - represent 1KB .*/

Tst_DDR_CTL->DENALI_CTL_194 |= 0x90001;